图灵完备1

德摩根定理

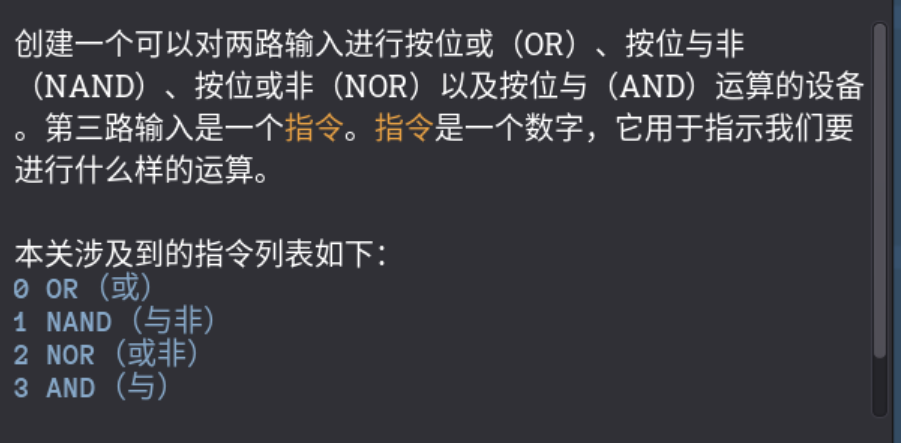

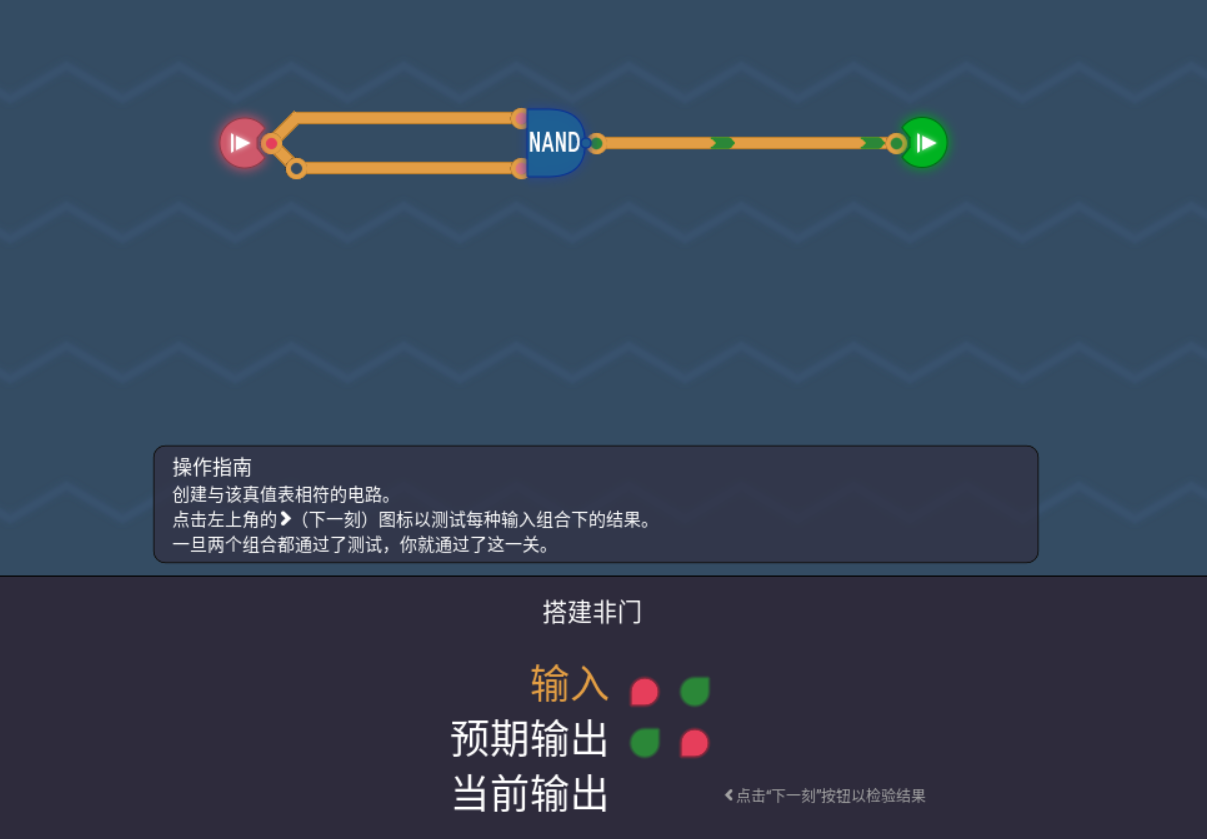

非门(与非门构建非门)

与非门可以当非门用,将两个引脚连输入

与非门的真值表是 1110,所以只需要将单端的输入连上与非门的两个引脚,输入 00 与 输入 11 所对应的结果是 1 与 0,效果和非门相同

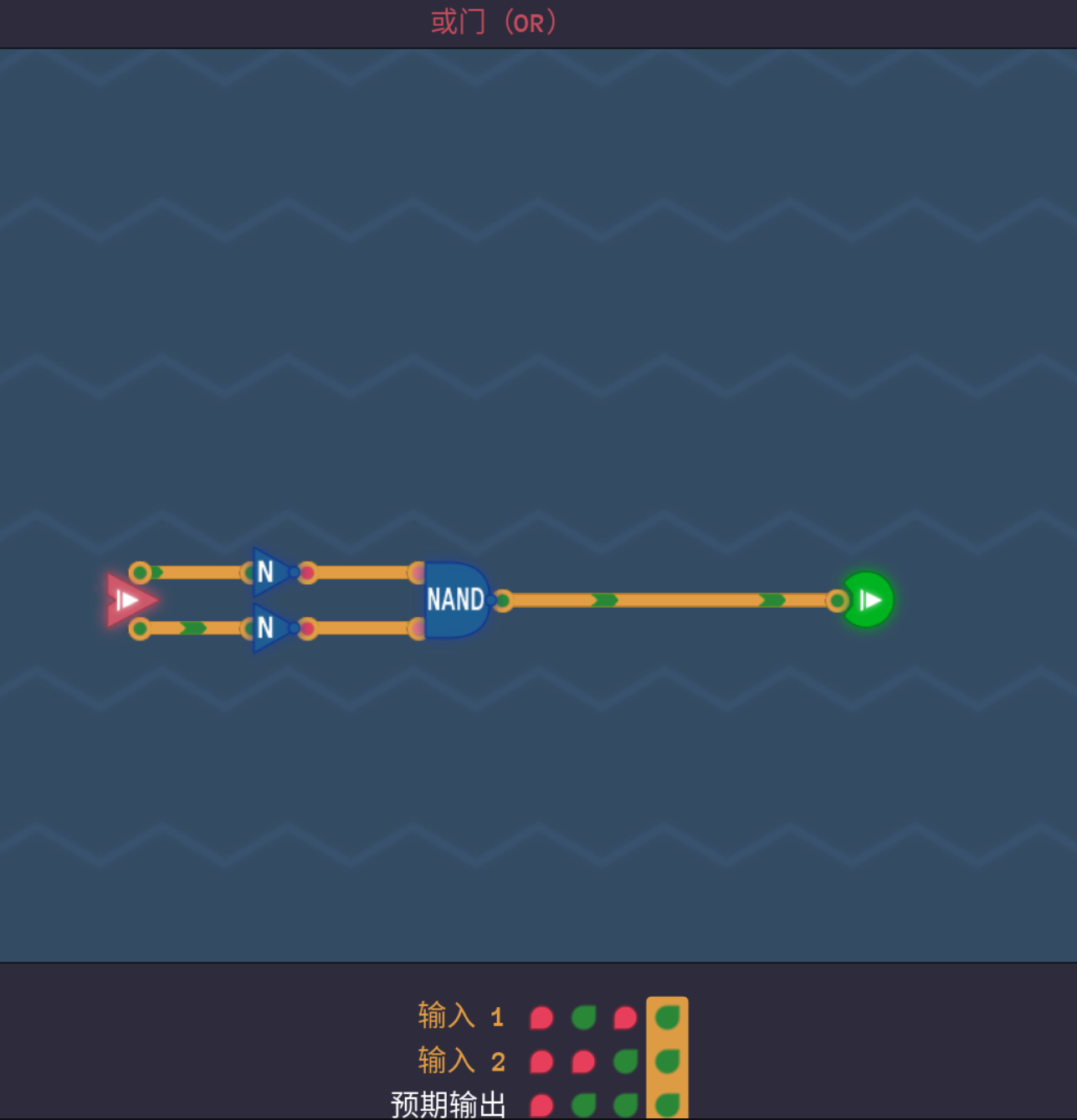

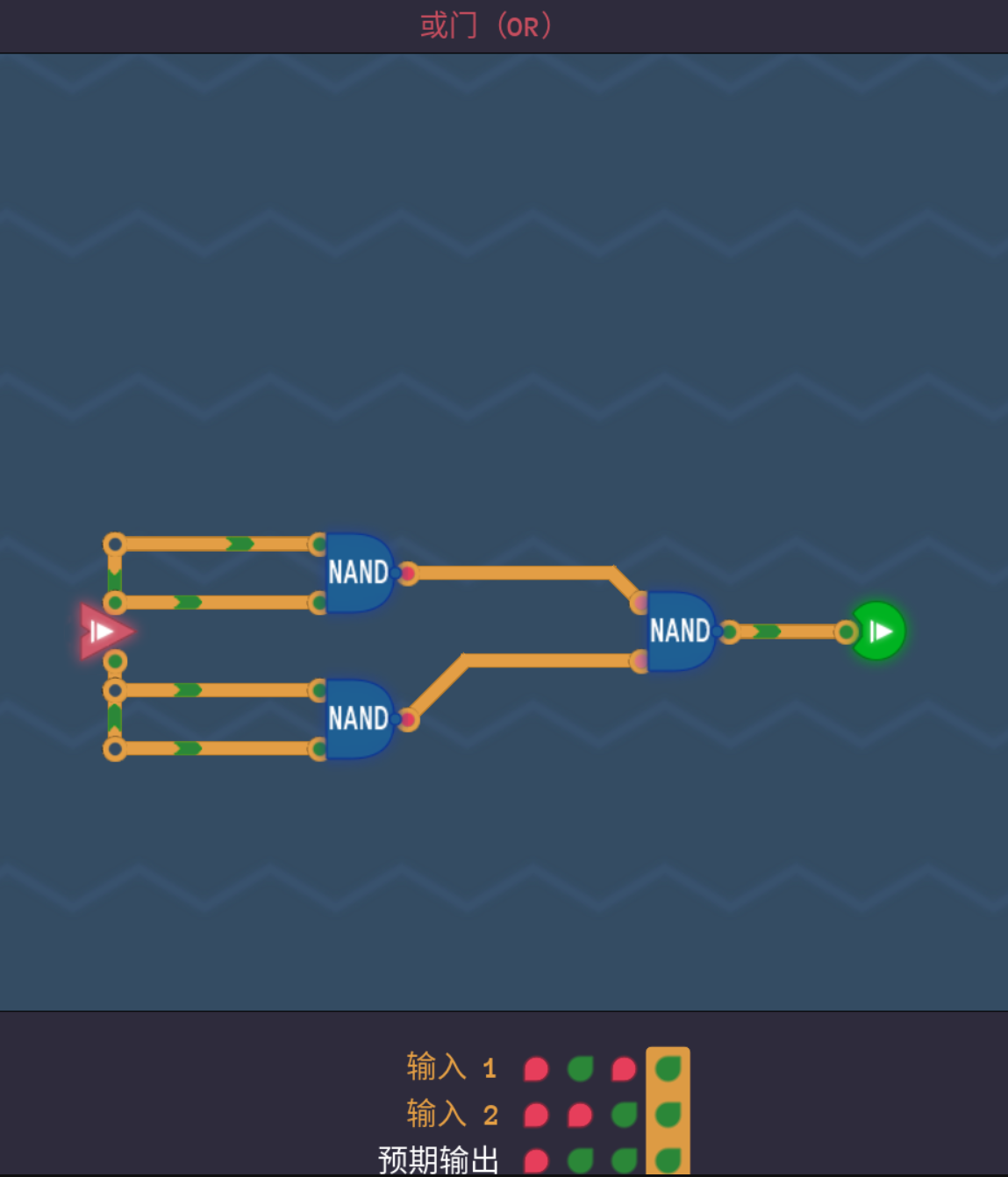

或门(与非门构建非门)

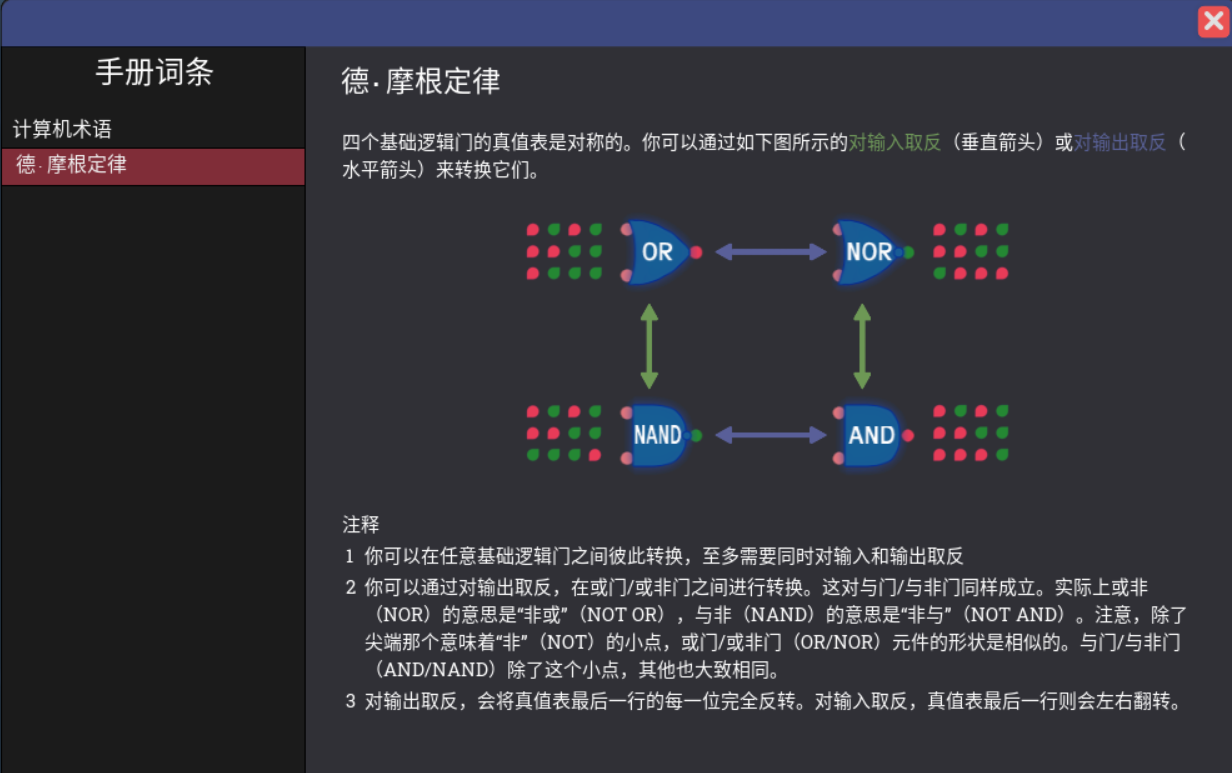

德摩根定理,在某个电路输入那串上非门,那输入序列顺序就会置反,使得真值表水平翻转,在某个电路输出那串上一个非门,输出信息的二进制位会置反

用之前与非门构建非门的思路来替代非门,三个与非门构建一个或门

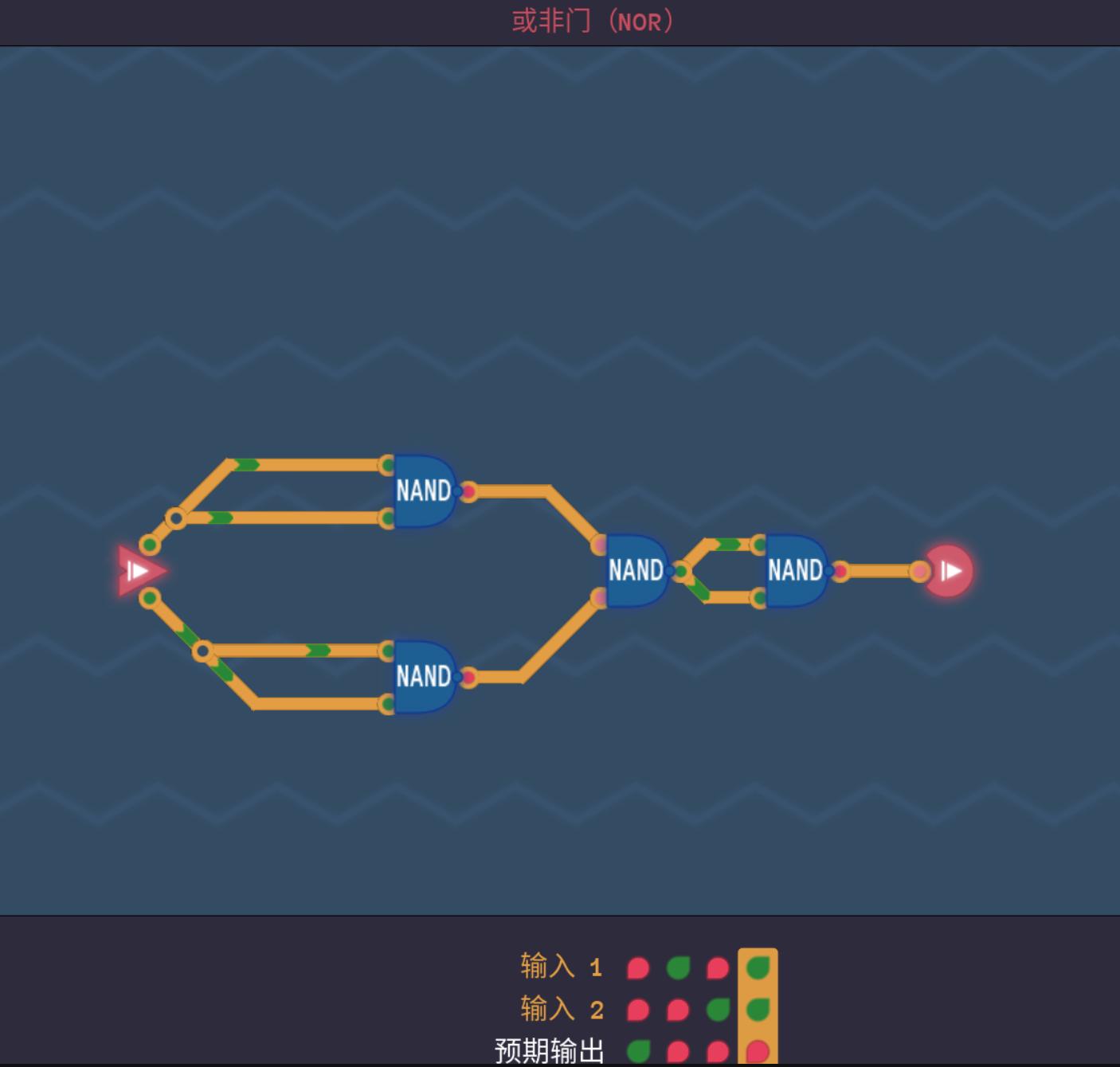

或非门(与非门构建或非门)

与非门的真值表是 1110 或非门的真值表是 1000,通过德摩根定理在输入那串上一个非门使得真值表水平翻转变成0111,之后在输出那串上非门来实现四与非门构建或非门

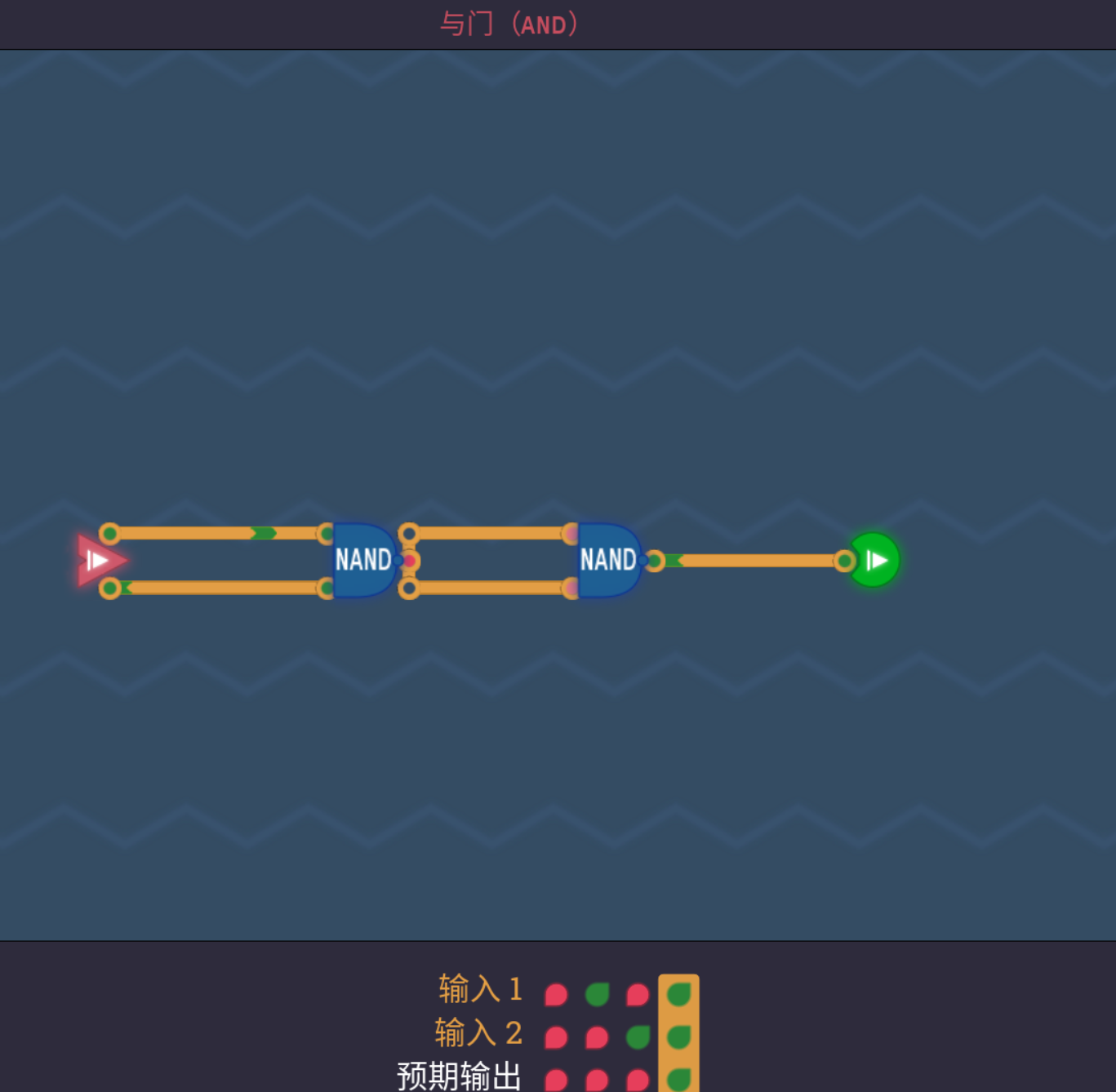

与门(与非门构建与门)

将与非门的输出置反得到与门

高电平

A or NOT(A) = 1

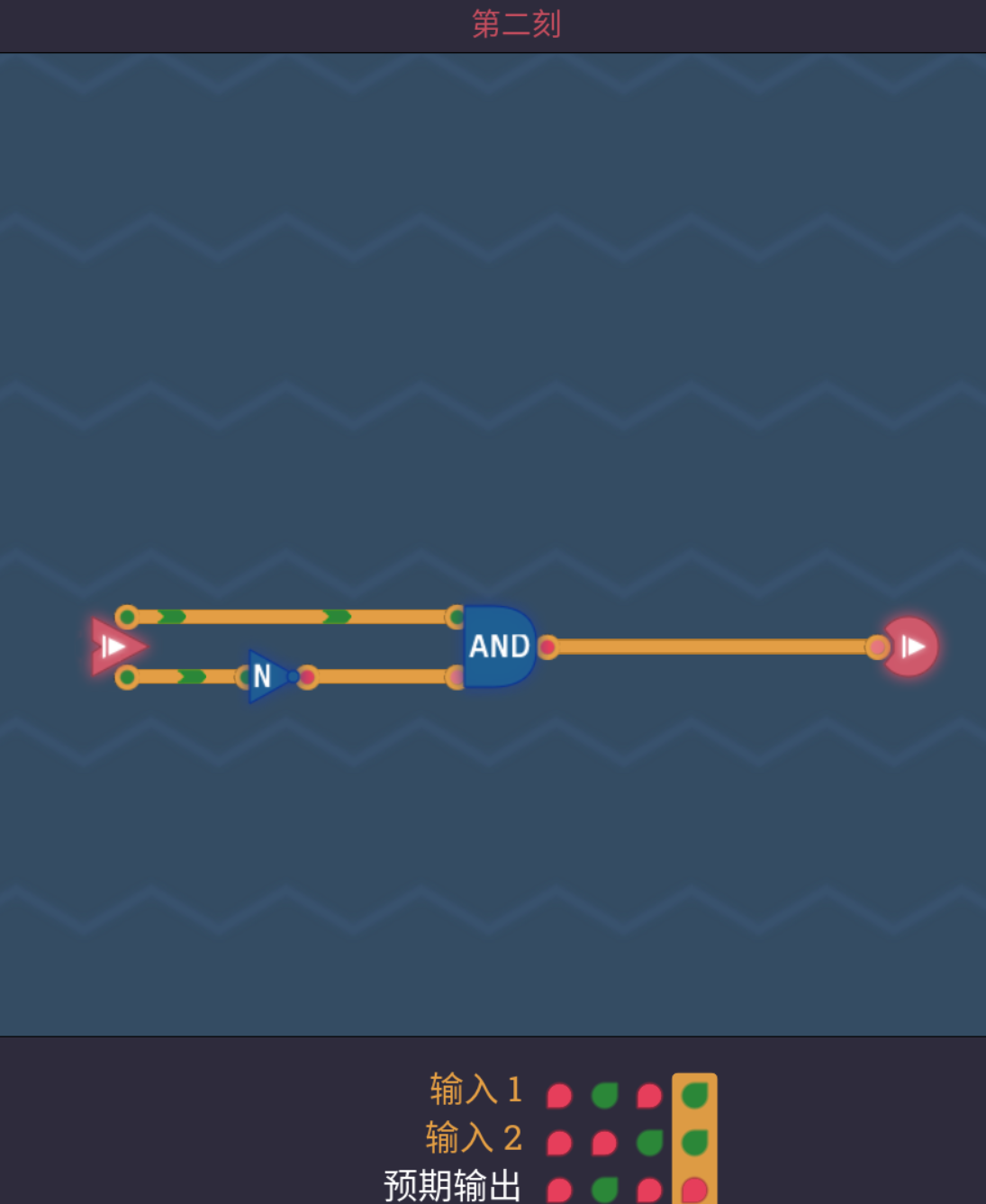

第二刻

只有一个最小项

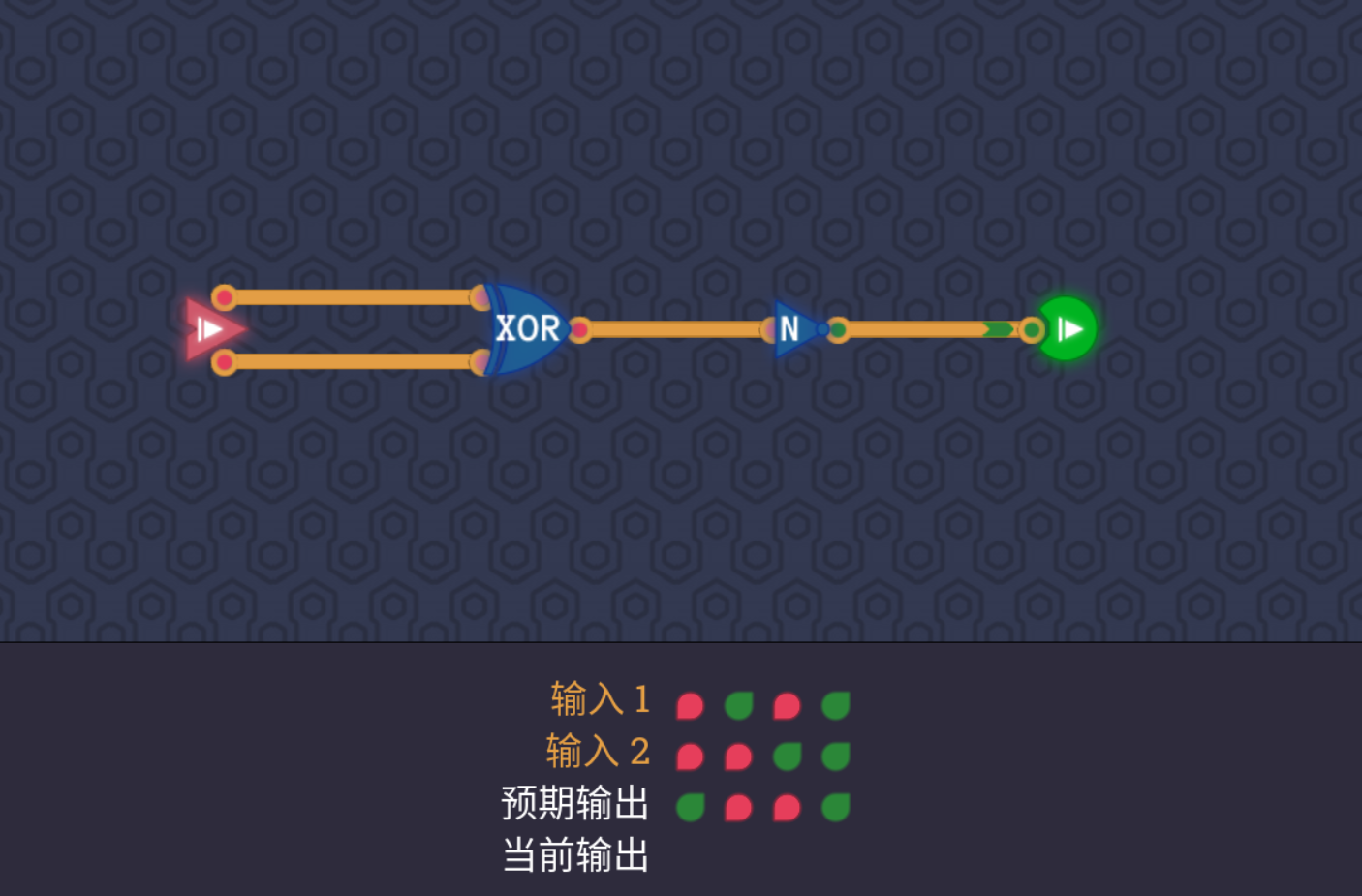

异或门

四与非门构建异或门

三输入或门

三输入与门

同或门

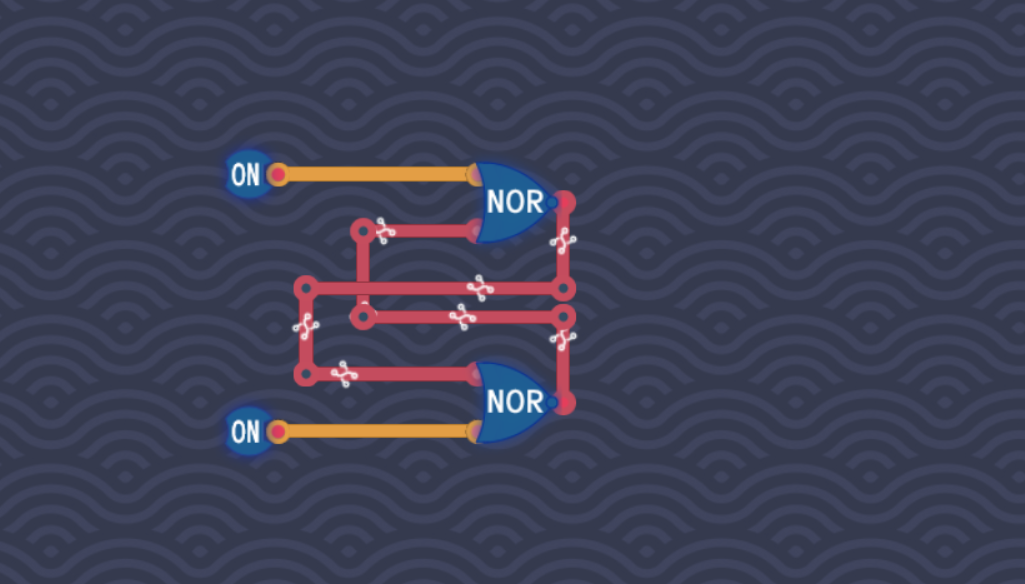

循环依赖

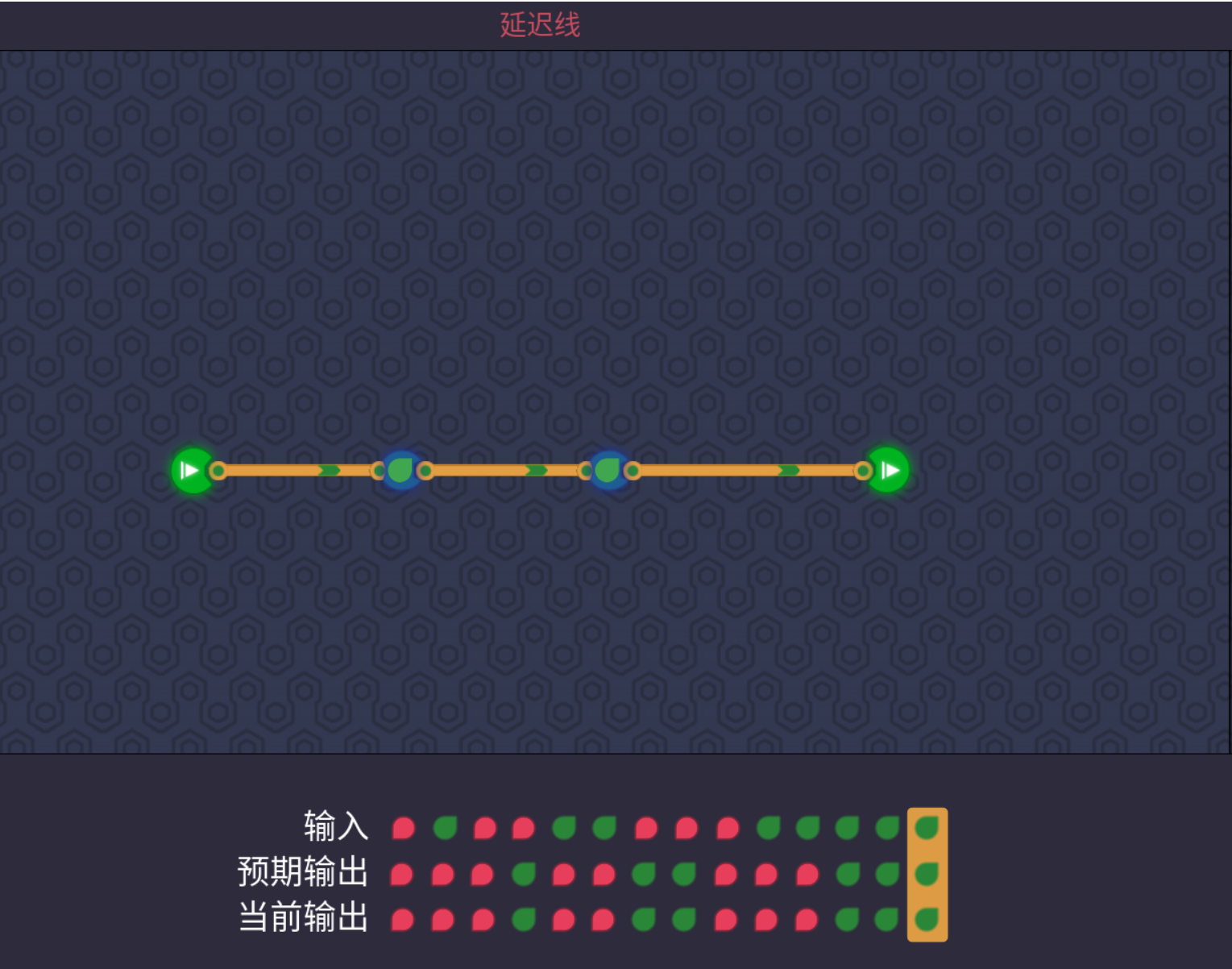

延迟线

延迟线可以将输出延迟一刻输出

奇偶不变

NOR 或非门本质上是一个带控制端的非门,当控制端为0时和非门等价,当控制端为1时,恒等输出0,通过延迟线将上一时刻的输入当做控制端就可以实现一个奇偶时刻输出相反的器件

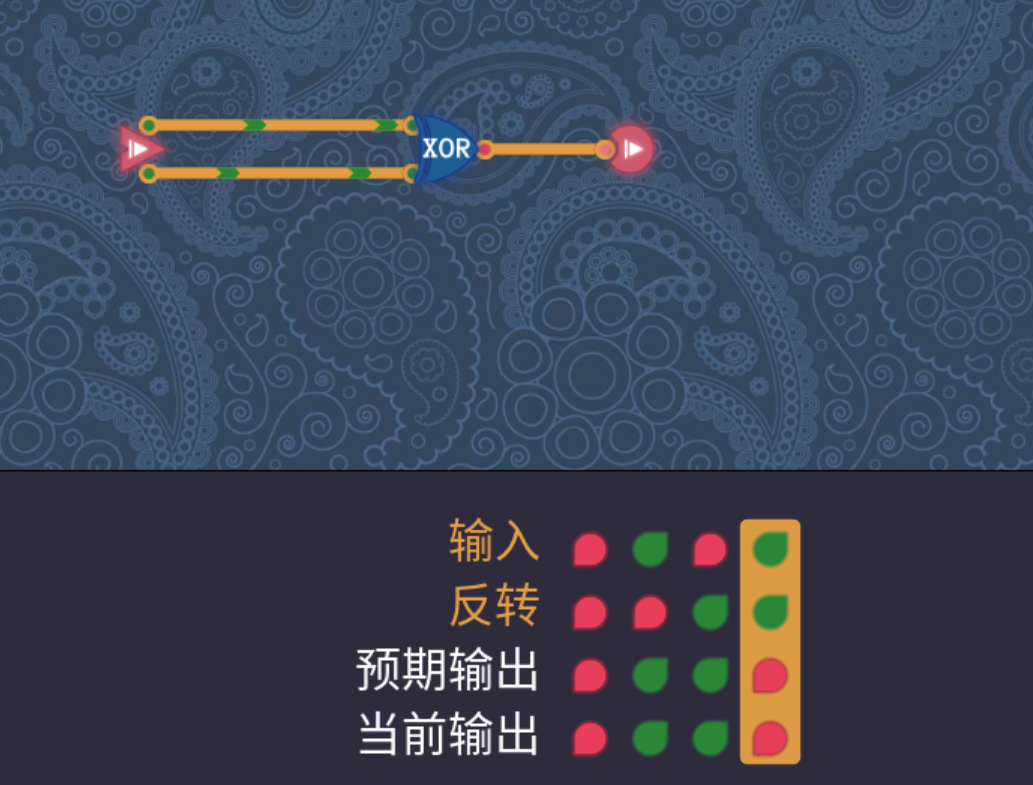

一位取反器

异或0不变,异或1置反输入的二进制位,所以异或可以实现一位的取反器

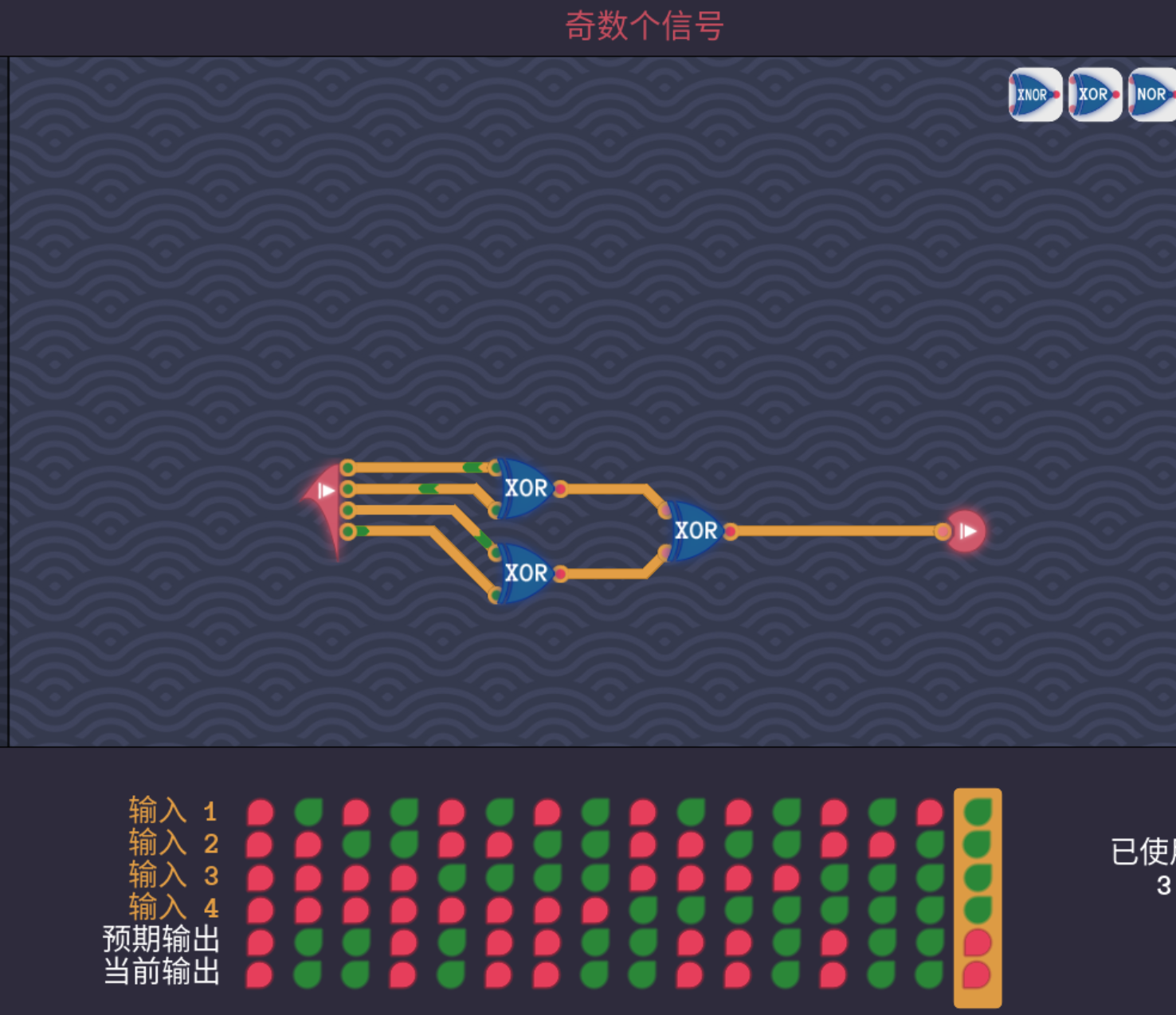

奇数个信号

只要满足输入1 2或者是输入 3 4中高电平的数量为奇数个那总体就是奇数个信号

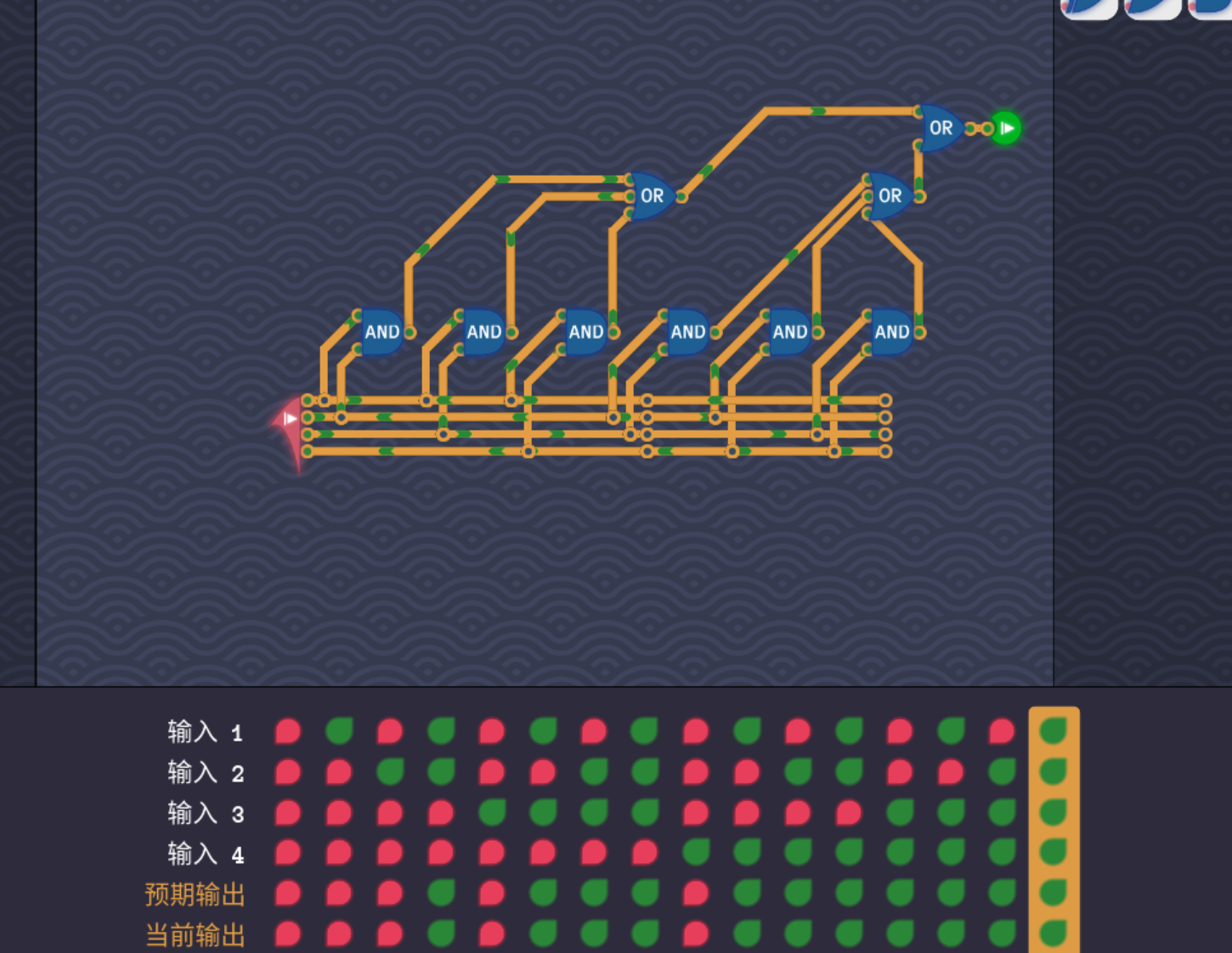

成对的麻烦

当高电平数量大于等于2时候输出为1

通过二元与运算涵盖所有的二元组序列,只要其中一个子运算结果为真,一共3+2+1个子序列,那高电平的数量一定大于等于二

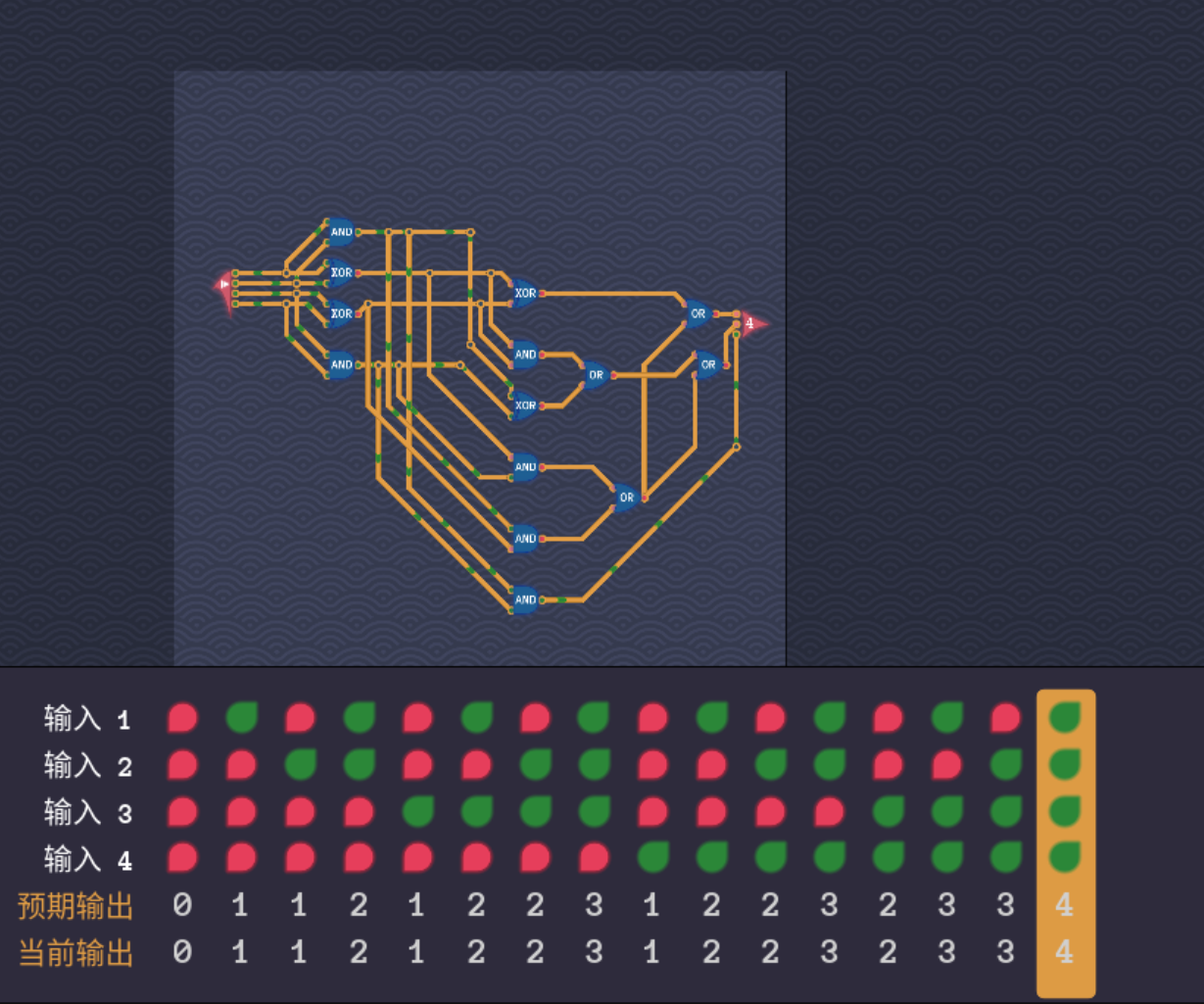

信号计数

二输入与门可以用来判断 输入高电平数量是否是偶数,异或门可以用来判断输入高电平数量是否是奇数

判断输入高电平数量是否为1 小计需要三个异或门 A XOR B XOR C XOR

判断输入高电平数量是否为2 有两种情况 一种是A B 或者 C D其中一组都为高电平,另一种是 A C 或者 A D 或者B C 或者 B D其中一组为高电平,前者用逻辑运算概括也就是 AB + CD ,后者只需要用异或就能概述 A XOR B + C XOR D

判断输入高电平数量是否为3 有两种情况 一种是 AB为真 C或D其中一个为真,另一种情况是 A或B为真,CD为真

所以 (A XOR B + CD) + (AB + C XOR D)

4就简单了 只需要用一个四输入的与门就可以判断。

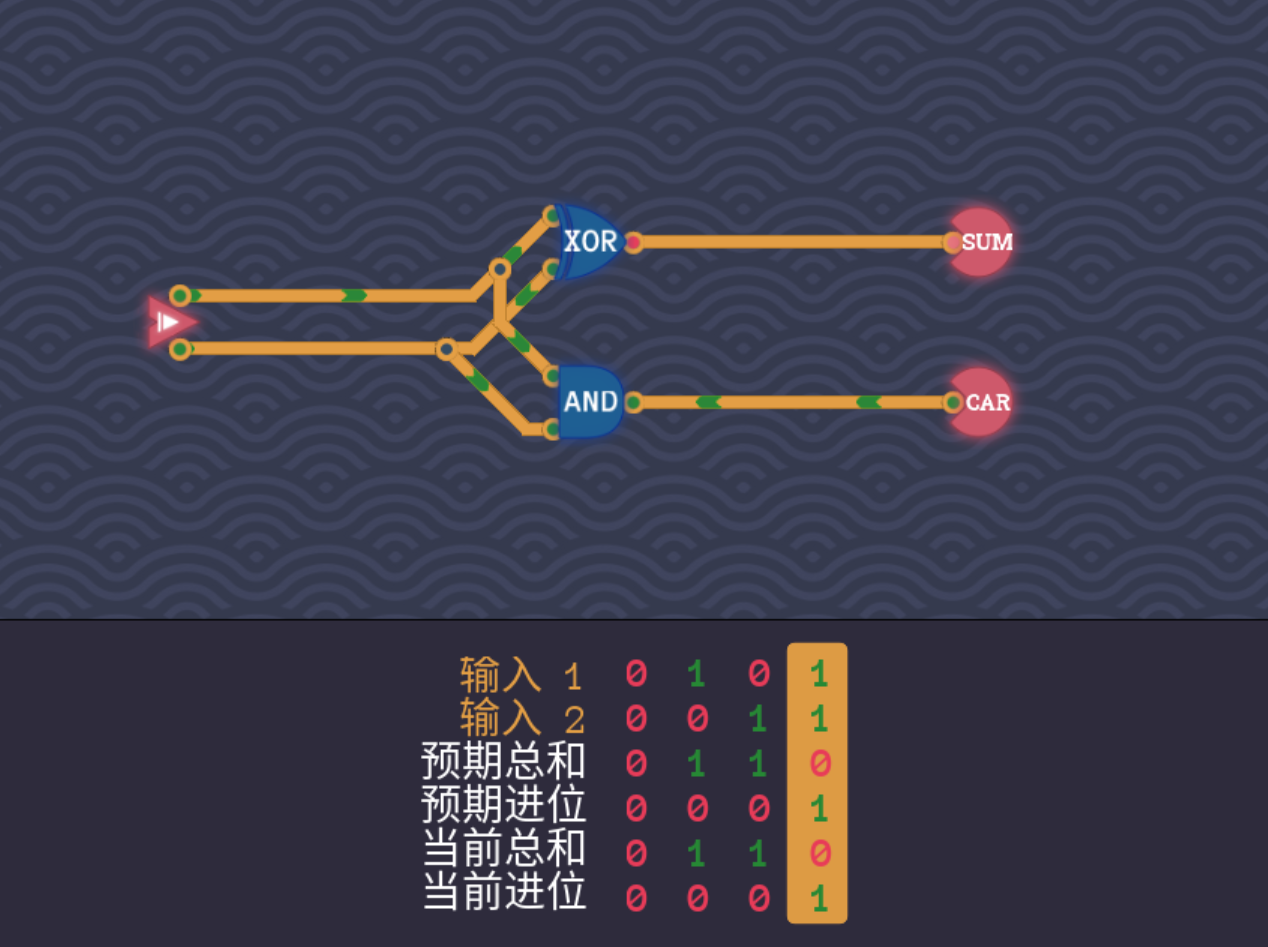

半加器

半加器是一种二输入二输出的器件,输入两个二进制数,输出进行加法后的结果和一个进位标志

当两个二进制数都为1时才会产生进位,所以进位的判断可以通过与门来判断,加法后的结果可以通过异或来计算,异或本质上是一个模2加法 A XOR B = (A + B) MOD 2s

半加器本质上是奇偶数判断问题,当高电平数量为奇数时 sum为1,当高电平数量为偶数时,进位标志位一

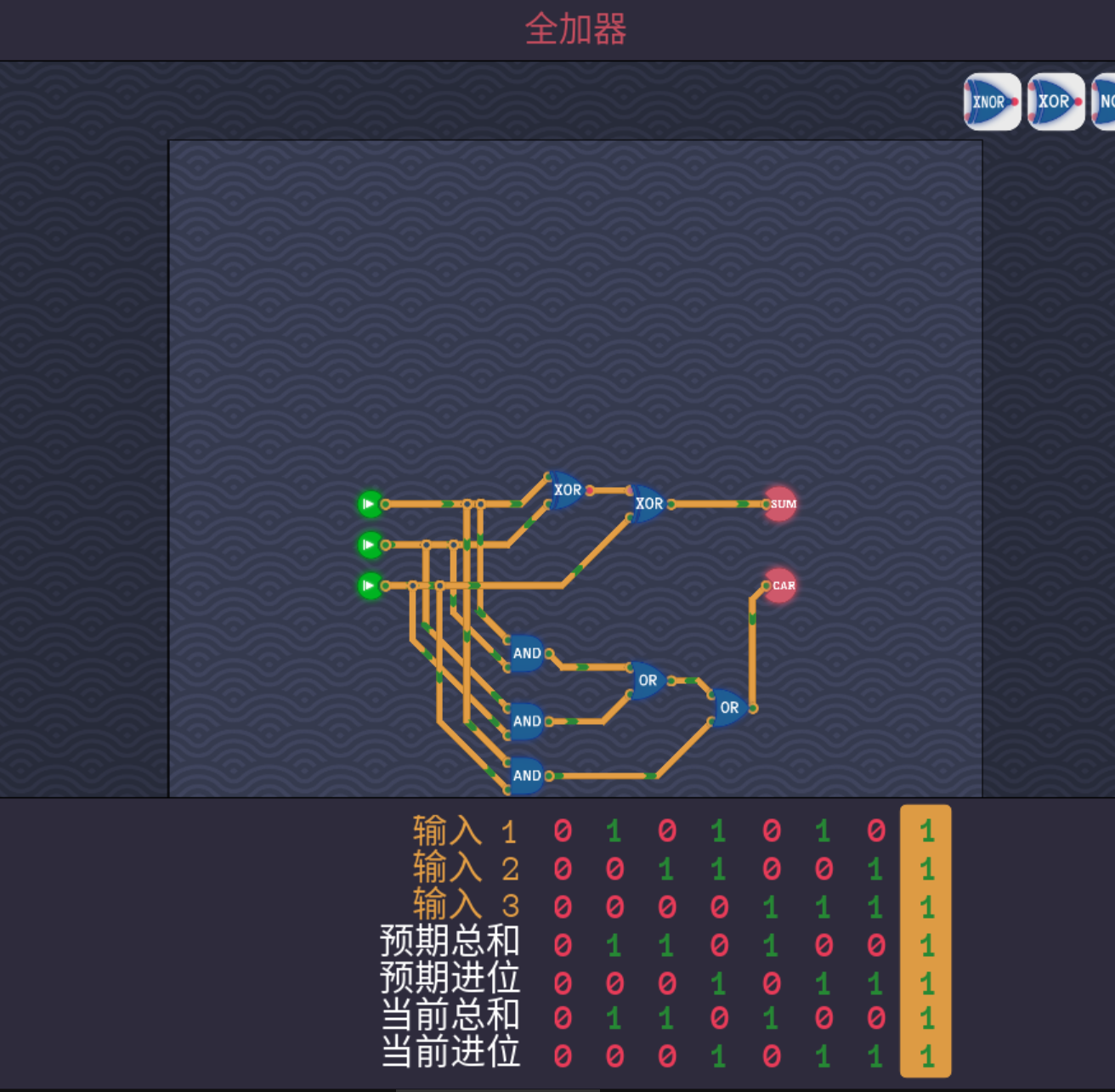

全加器

全加器本质上也是奇数和 输入高电平数量是否大于等于2这两个问题

当高电平数量为奇数时 sum = 1 ,通过三个xor来判断是否是奇数

大于等于2的判断只需要用与运算涵盖所有数量为2的唯一组合,之后满足其中一个条件那数量一定是大于等于2

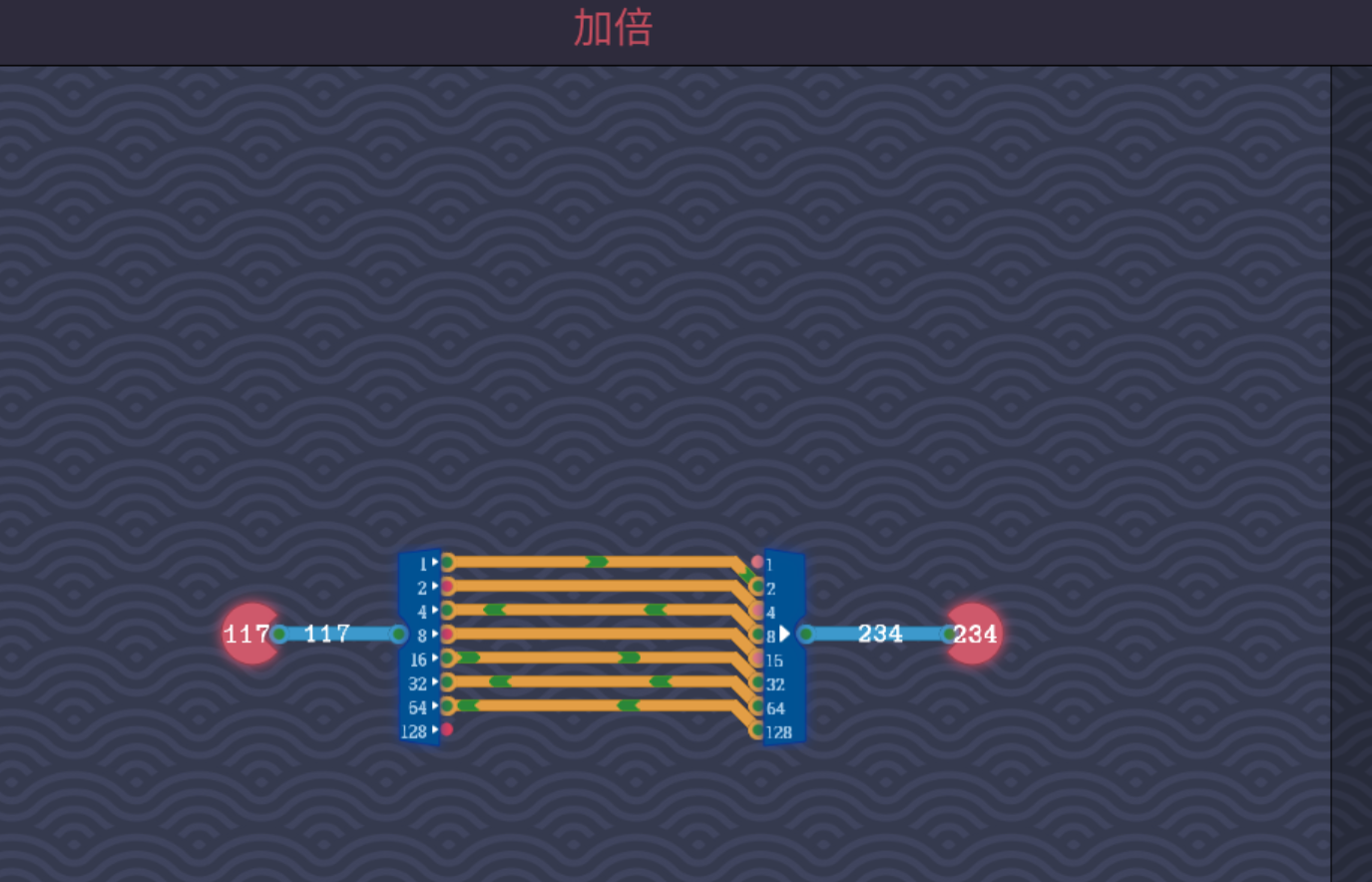

加倍

将分线器的端口按照左移一位的逻辑接入到另一个分线器的端口就可以实现翻倍

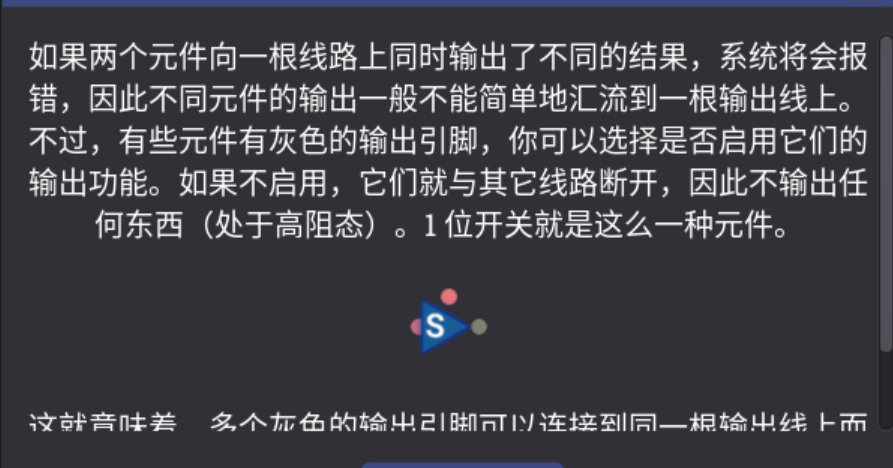

1位开关

从行为逻辑上来说1位开关和与门没有任何区别,当两个输入为 00 01 10时开关,有两组输入开关会保持断开的状态,有一组输入开关保持打开但是输出的是低电平信号,所以和与门差不多,将多组开关状态是互斥的1位开关并联和非门的行为相似

NOT(A)B + ANOT(B)

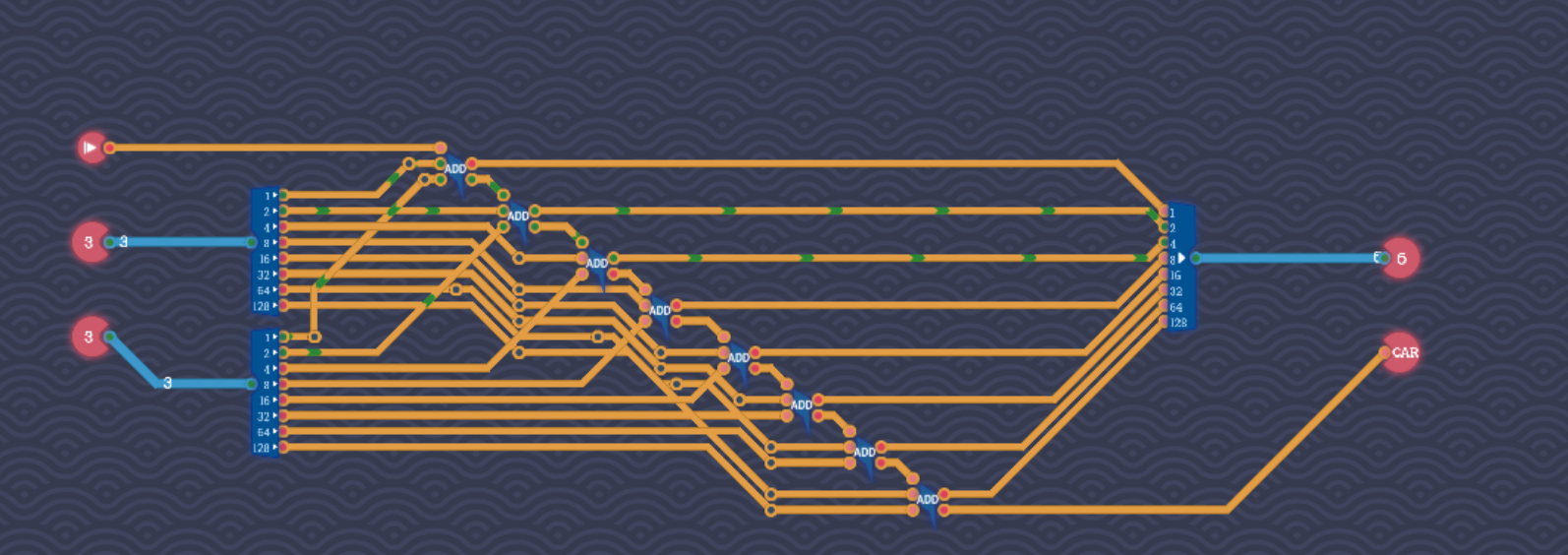

8位加法器

行波进位加法器,通过八个全加器构建八位加法器,每个全加器产生的进位输出作为一个数据位传递给下一个全加器进行三位数加法运算来实现八位的加法

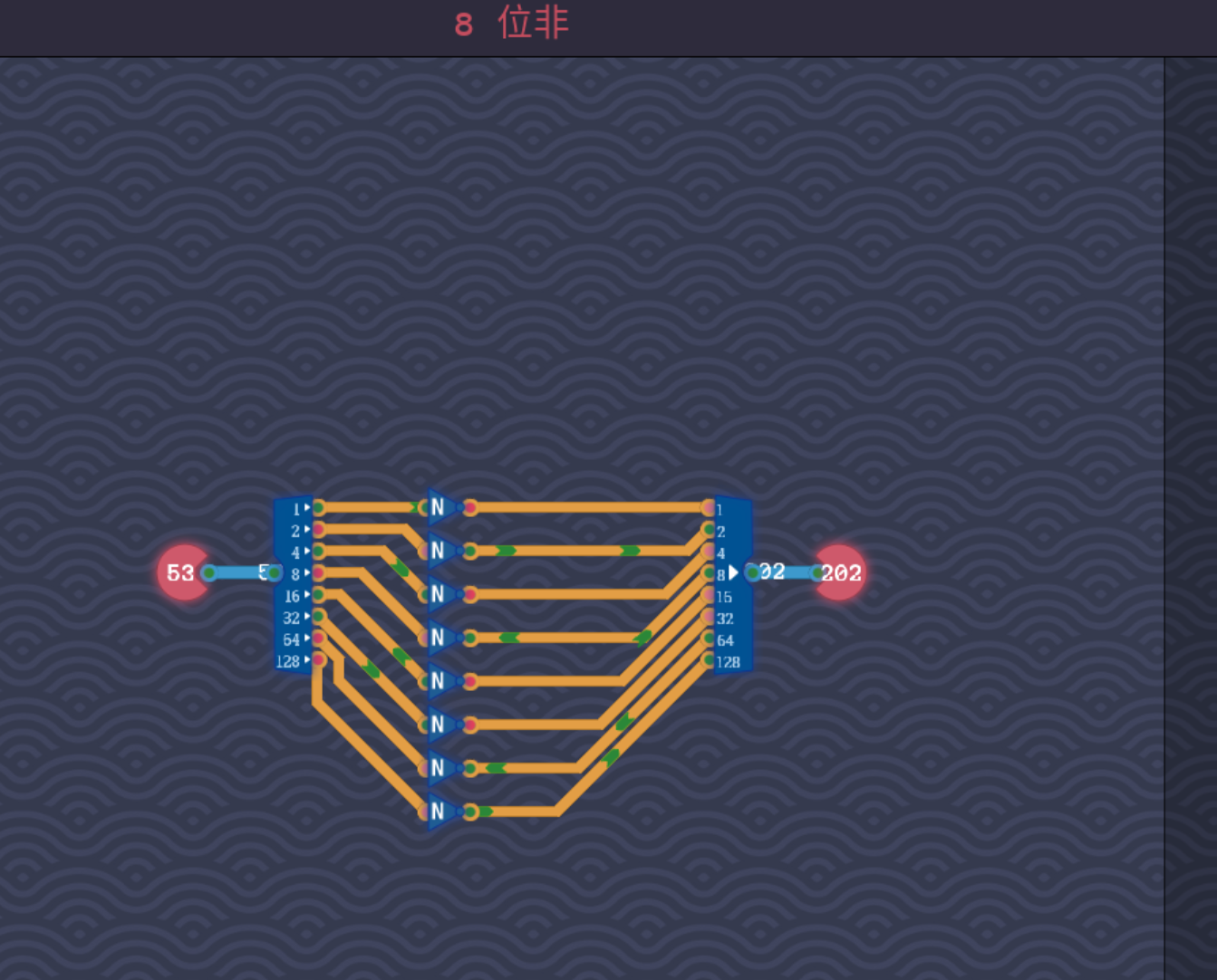

8位非

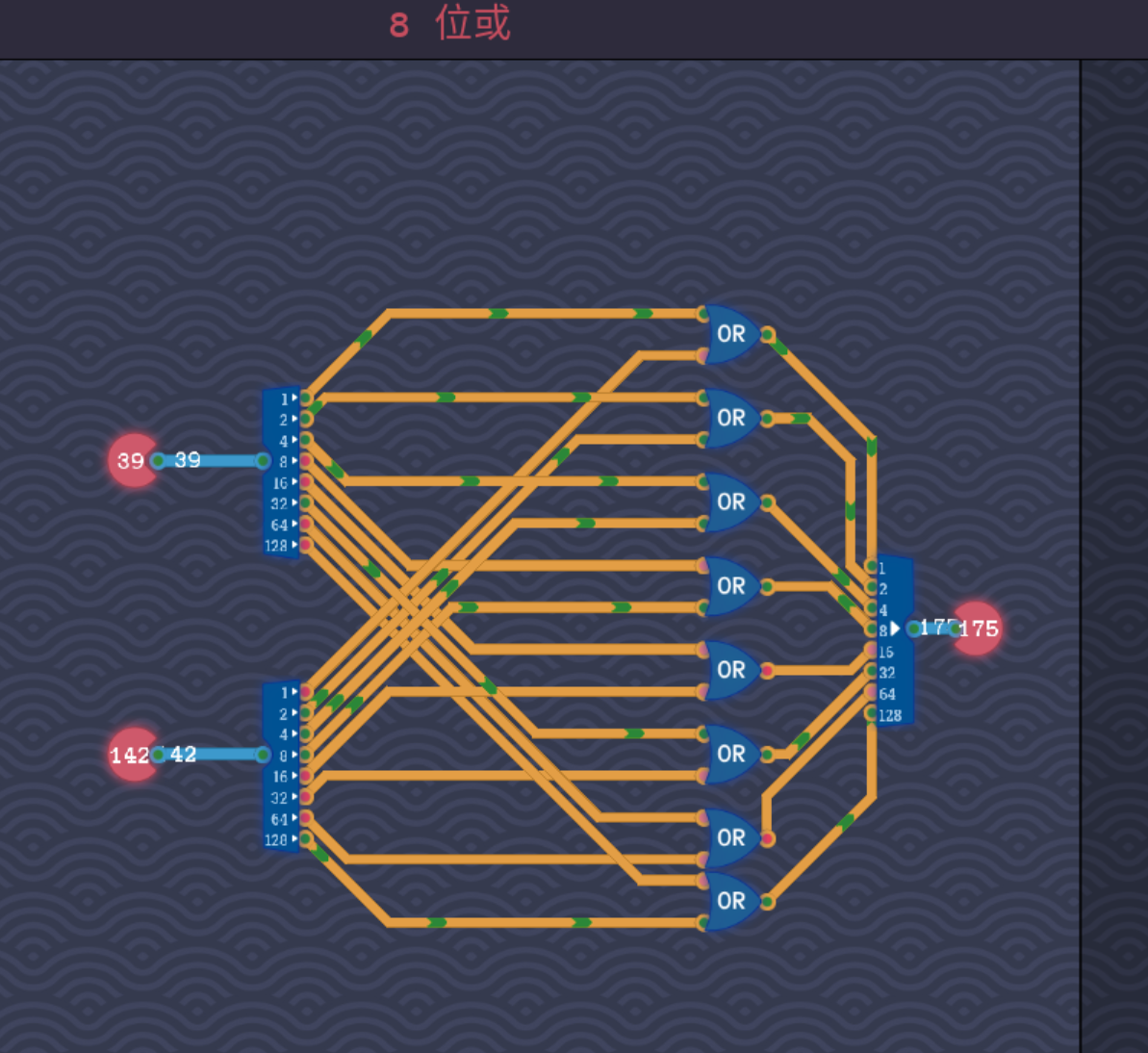

8位或

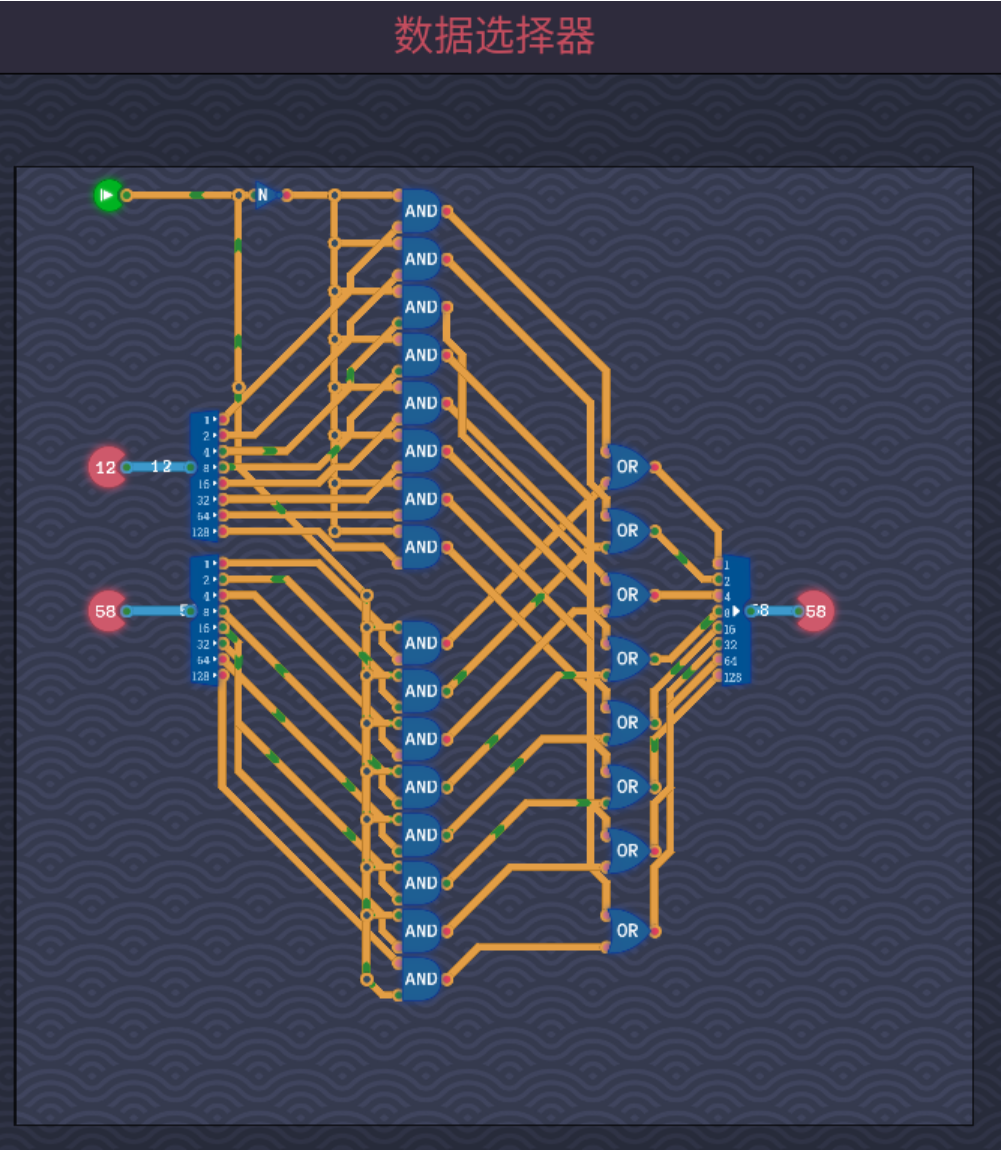

数据选择器

二选一选择器工作原理 NOT(S)A + SB,只需要通过分线器和集线器对八个比特位套用二选一选择器就行

相反数

补码中正负数转换就是取反+1

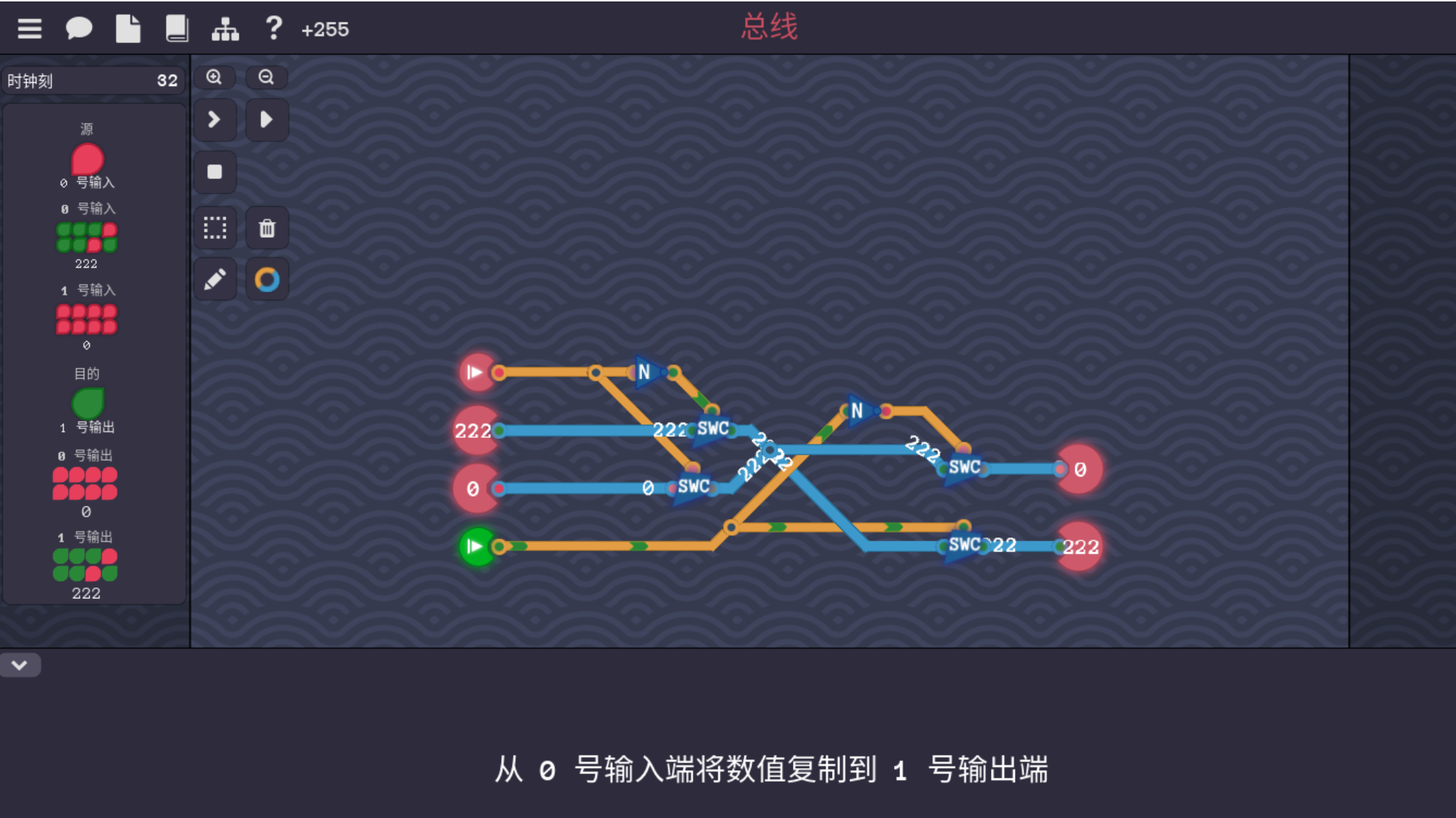

总线

通过非门来实现类似于二选一选择器的功能来控制八位开关的打开和关闭去实现 数据的”复制” 本质上就是一个选择器来实现开关信号的互斥

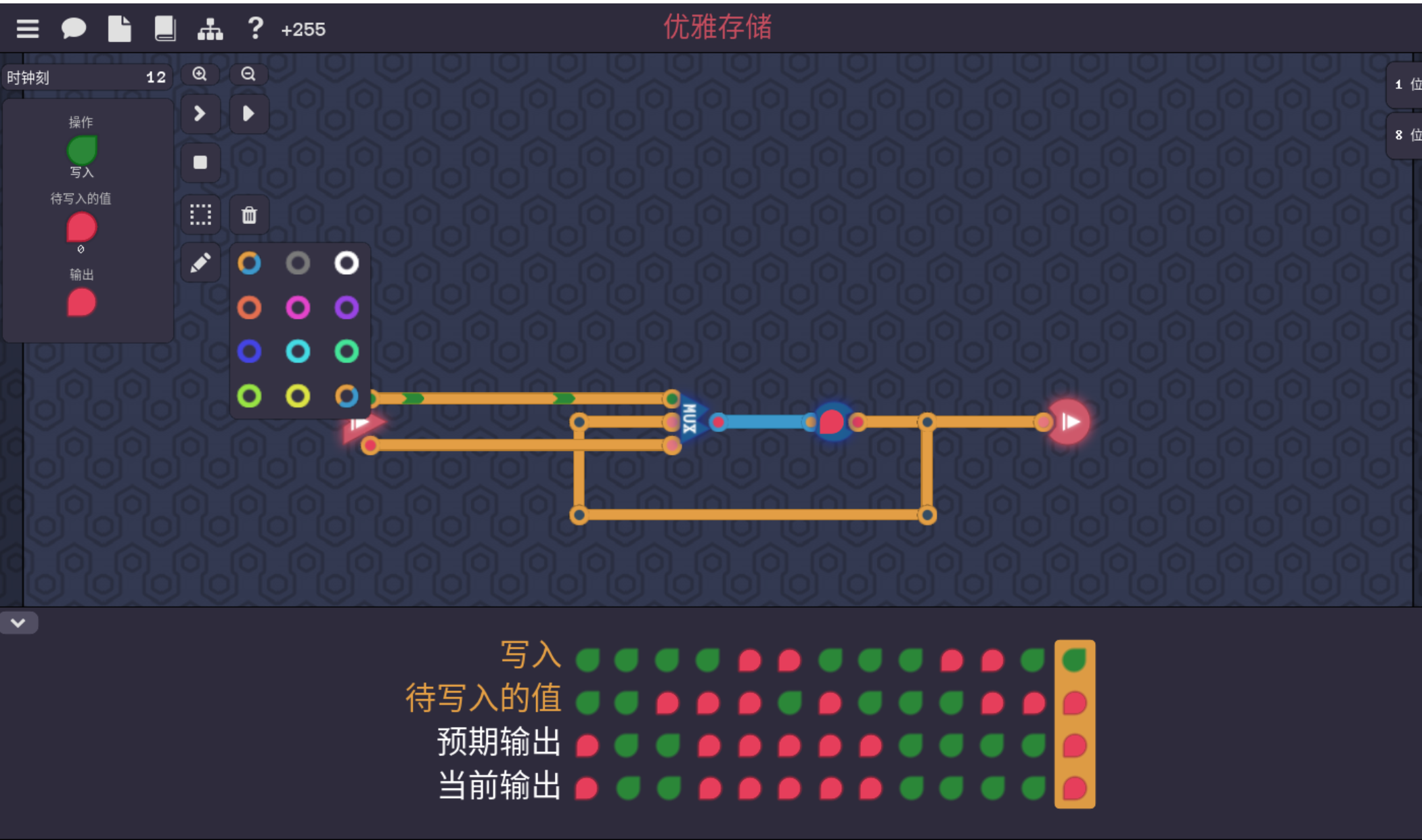

优雅存储

如果将延迟线的首尾连接就可以实现以后存储一位的功能,比交叉配对反相器效率还高(

通过二选一选择器来实现一个控制器,当控制信号为写入信号时就通过mux的切换来实现往存储器件里写入1位数据

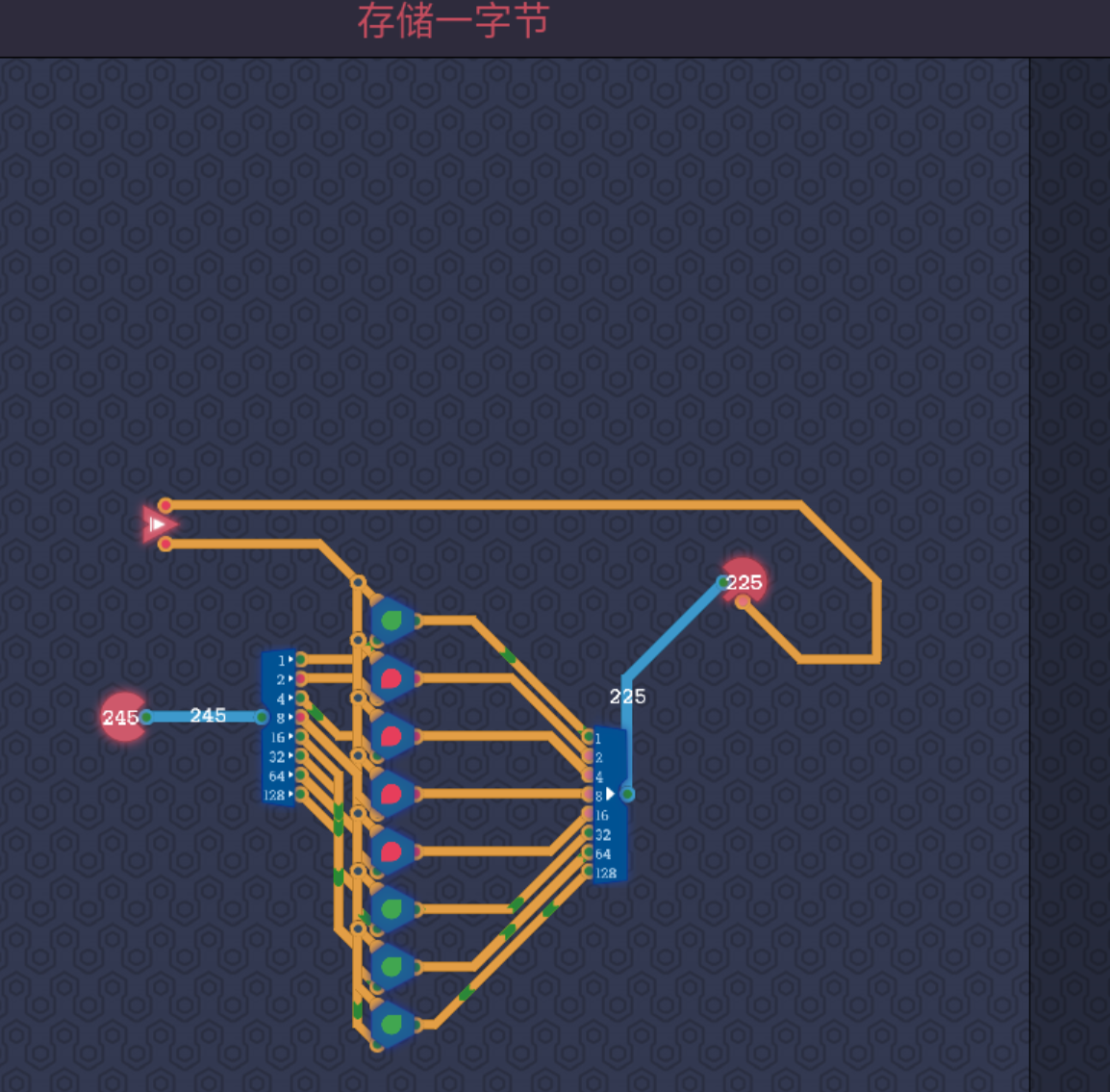

存储一字节

1位解码器

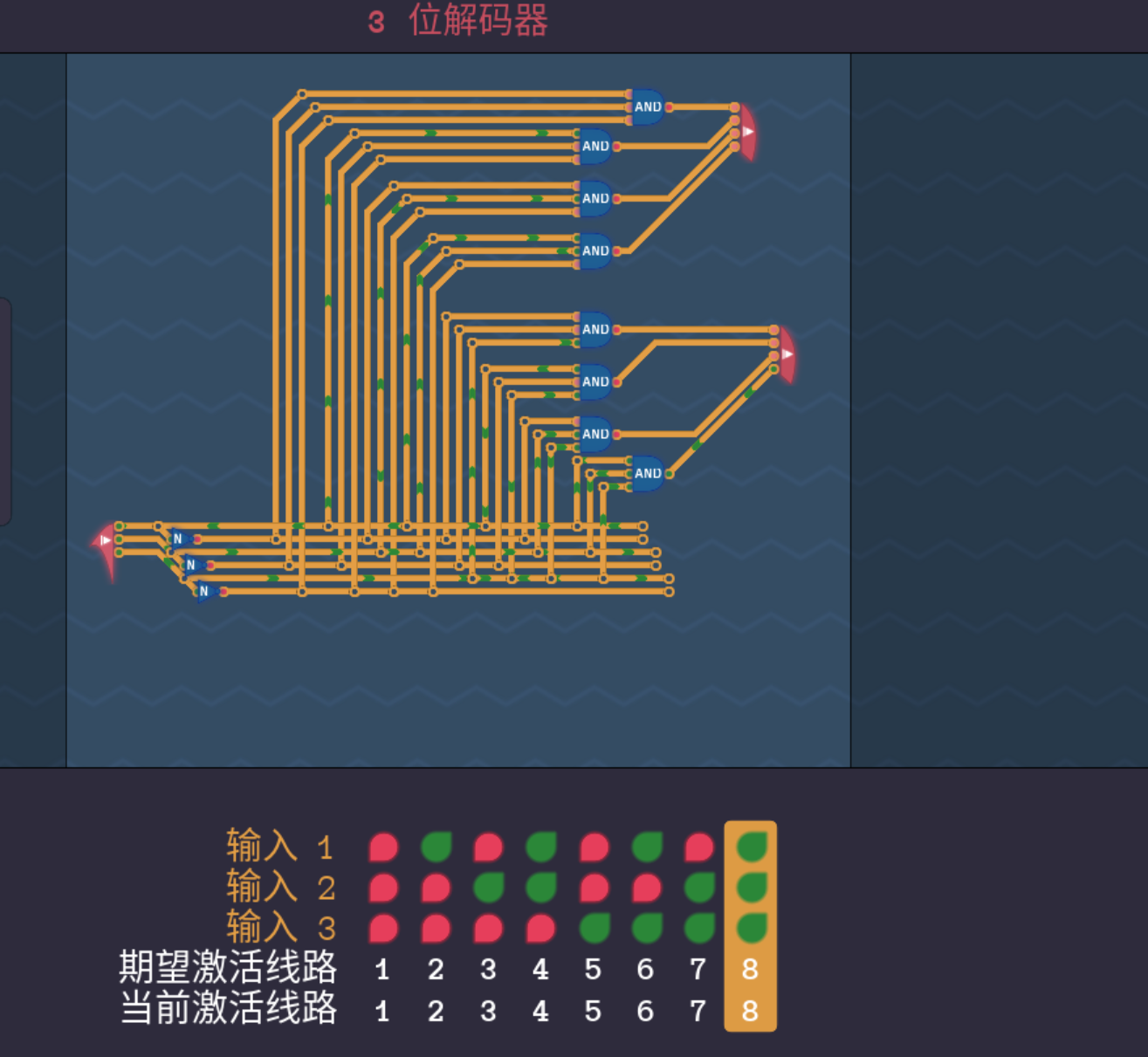

3位解码器

逻辑引擎

通过三位译码器生成四组使能信号来分别表示四种逻辑运算,之后将这四组使能信号分别作为四个八位开关的控制端输入,八位的逻辑门只有或门和非门,可以通过德摩根定律来搓出与门和与非门