ysyx_f3数电基础

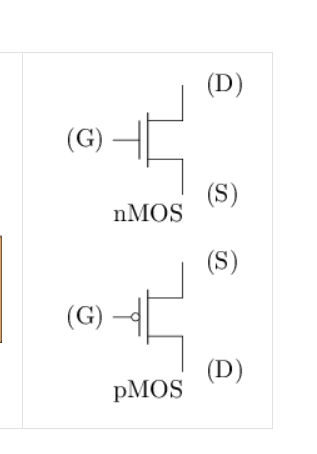

cmos中的nmos和pmos

nmos和pmos在电路图上的表示符号

当Vg- Vs较大时 nmos是的源极漏极是导通状态

当Vs - Vg较大时 pmos的源极漏极是导通状态

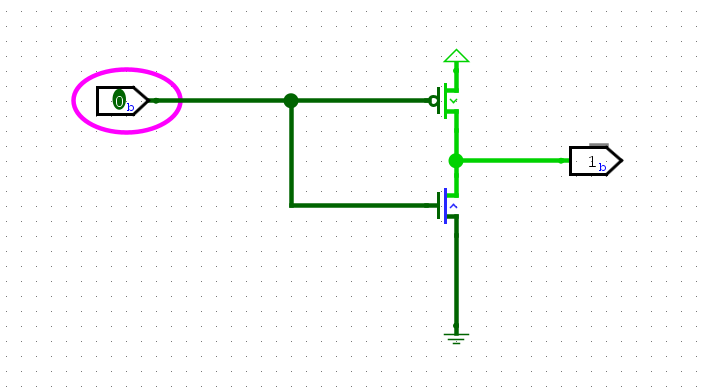

非门

非门是通过一个pmos和一个nmos组成的,输入是低电平时pmos中的Vs - Vg为较大值使电源和输出导通。当输入是高电平pmos不满足导通的条件,nmos满足。

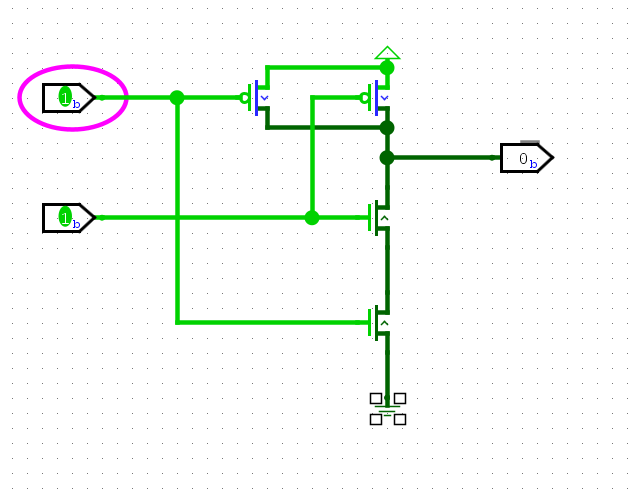

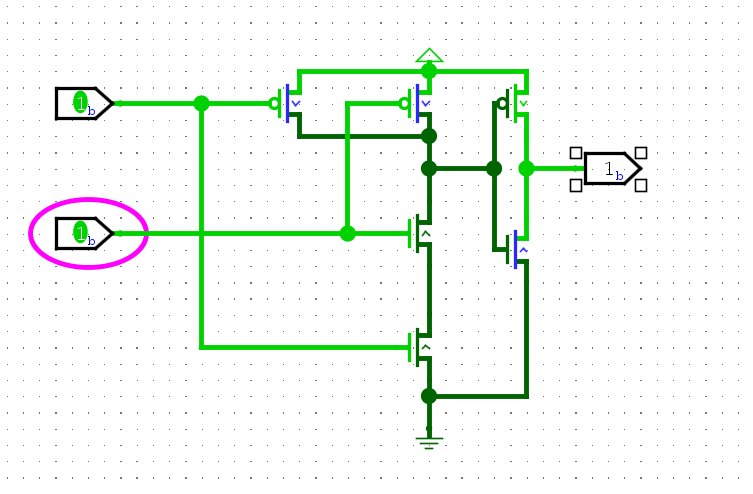

与非门

与非门的行为是当两个输入都不为1时输出1,相反。

与非门由两个pmos并联和两个nmos串联构成,当输入1和2都为0时,两个pmos均满足导通的条件,两个nmos均不满足导通条件,输出为1

输入和输出其中一个为0,另一个为1时候,其中一个pmos满足导通,其中一个nmos满足导通,由于nmos是串联的,pmos是并联的所以输出为1

输入和输出都为1时,两个nmos都满足导通条件,pmos都不满足导通条件,输出为0

与门

与门就是在与非门的基础上在输出位置加了个非门,将结果置反后就实现与运算了。

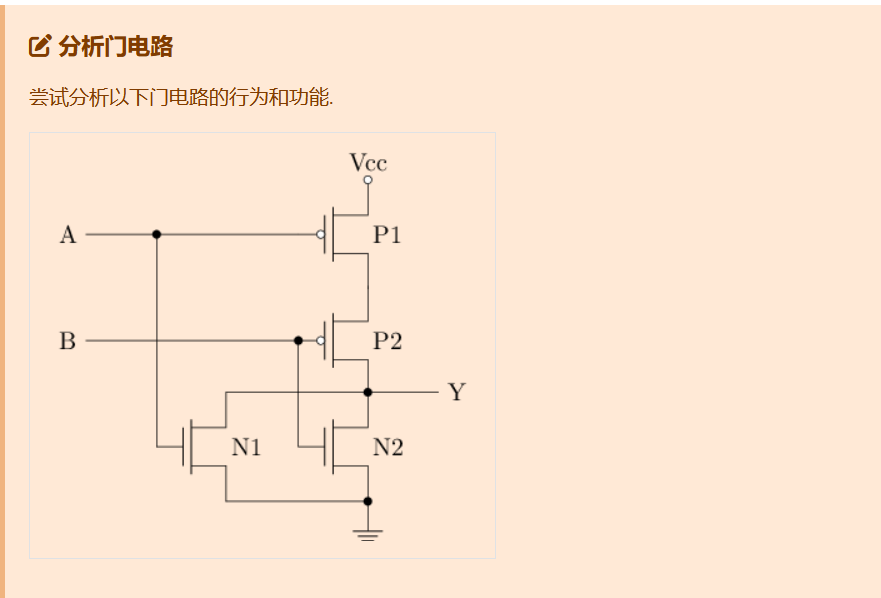

分析门电路

一共有2^2=4种输入状态

只有p1&p2同时导通的同时电源才会输出1,对于其他情况都是输出0,这是或非门

| A | B | P1 | P2 | N1 | N2 | Y |

|---|---|---|---|---|---|---|

| 0 | 0 | 导通 | 导通 | 截止 | 截止 | 1 |

| 0 | 1 | 导通 | 截止 | 截止 | 导通 | 0 |

| 1 | 0 | 截止 | 导通 | 导通 | 截止 | 0 |

| 1 | 1 | 截止 | 截止 | 导通 | 导通 | 0 |

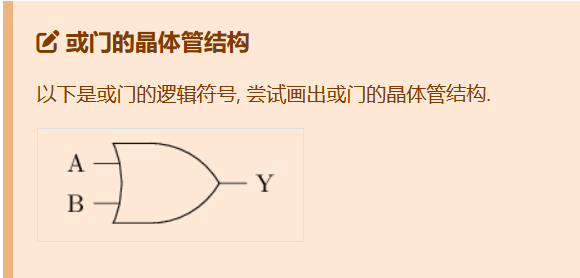

或门的晶体管结构

在或非门的基础上加上一个非门就能实现一个或门

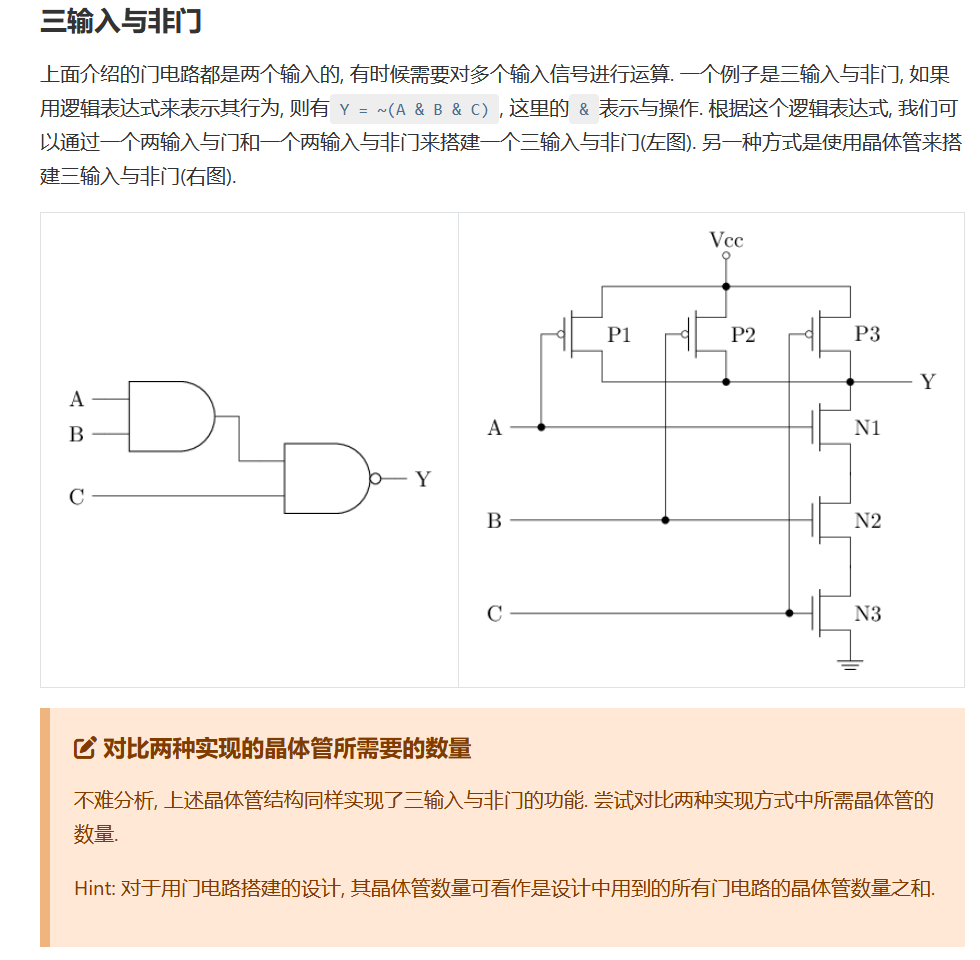

对比两种实现的晶体管所需要的数量

第一张图所需的晶体管数量是 6(与门) + 4(与非门) = 10,第二张图晶体管的数量是6

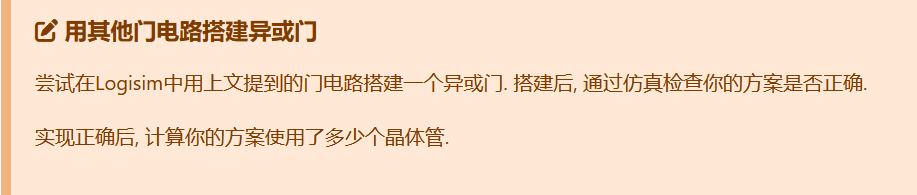

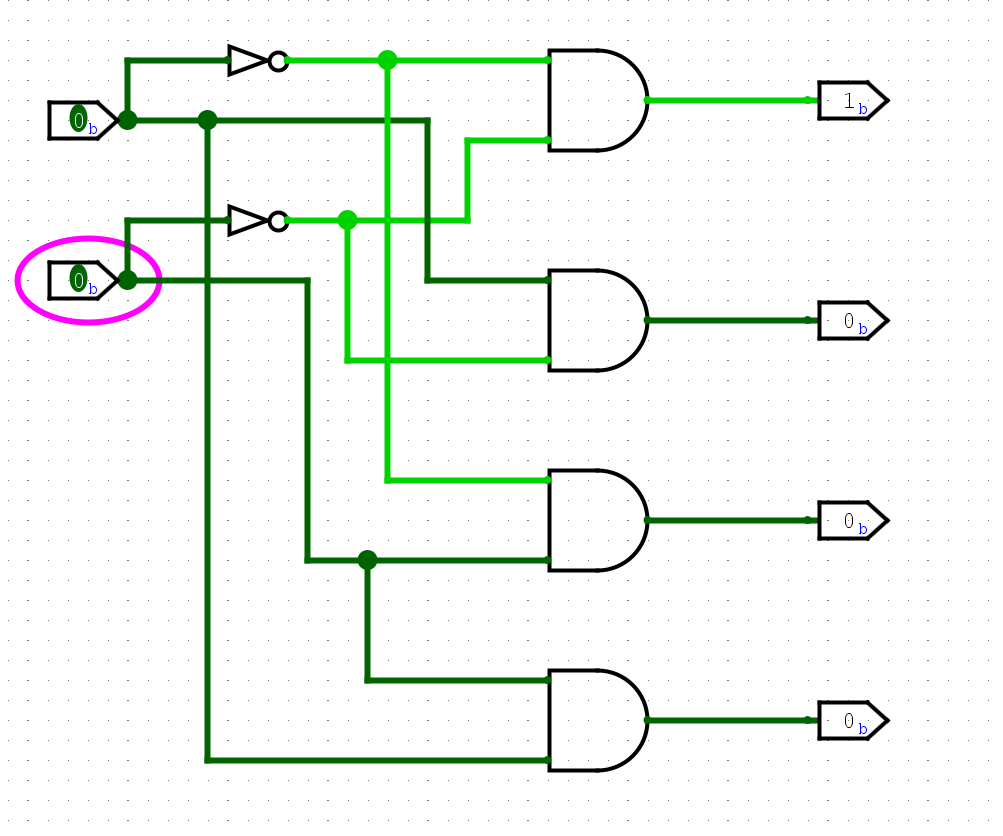

用其他门电路搭建异或门

A XOR B = (!A & B) | (A & !B)

一共用到 2 + 2 + 6 + 6 + 6 = 22个晶体管

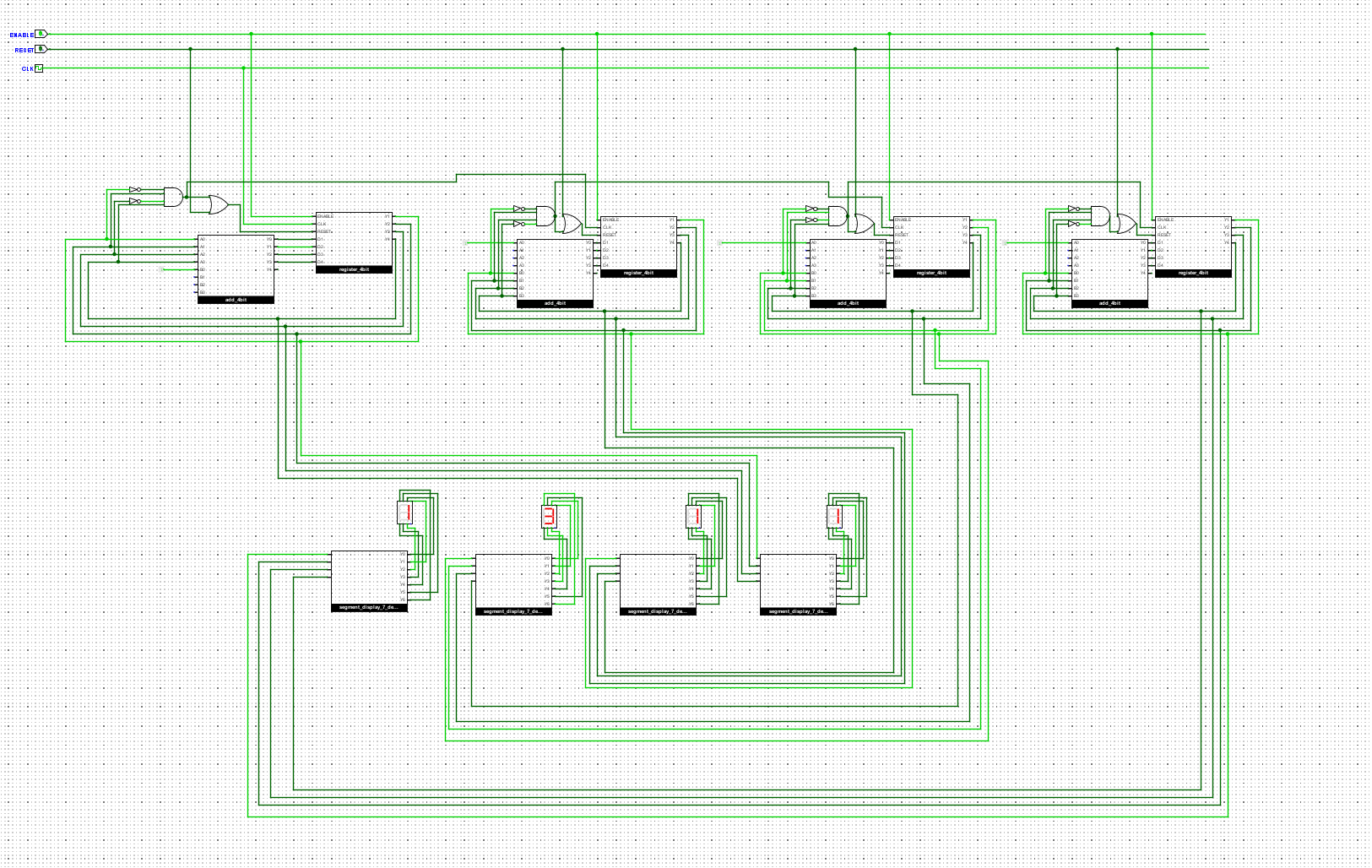

设计同或门

在异或门的输出那串一个not将输出置反就是同或门了

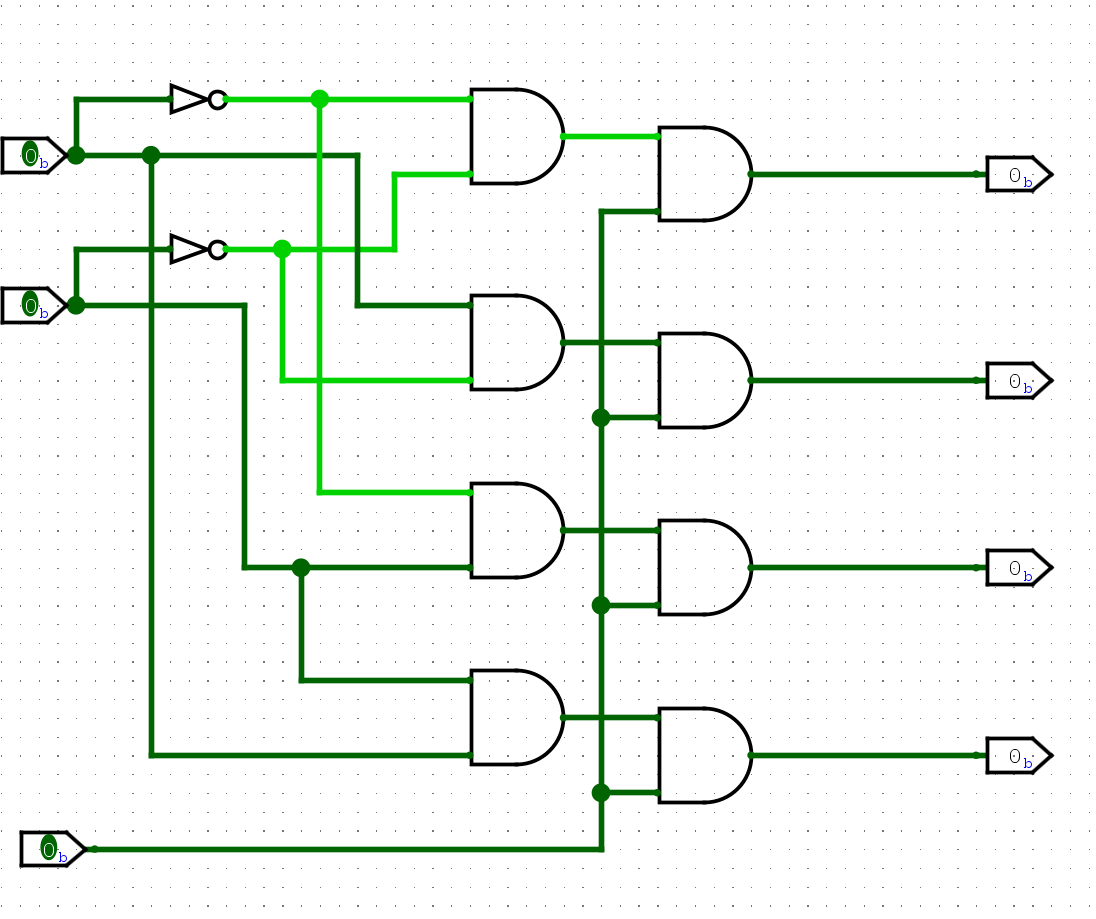

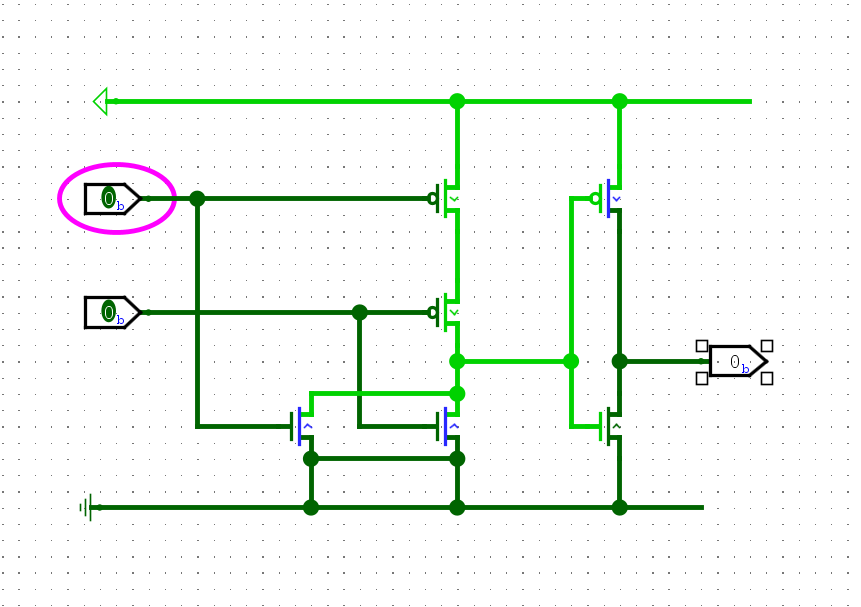

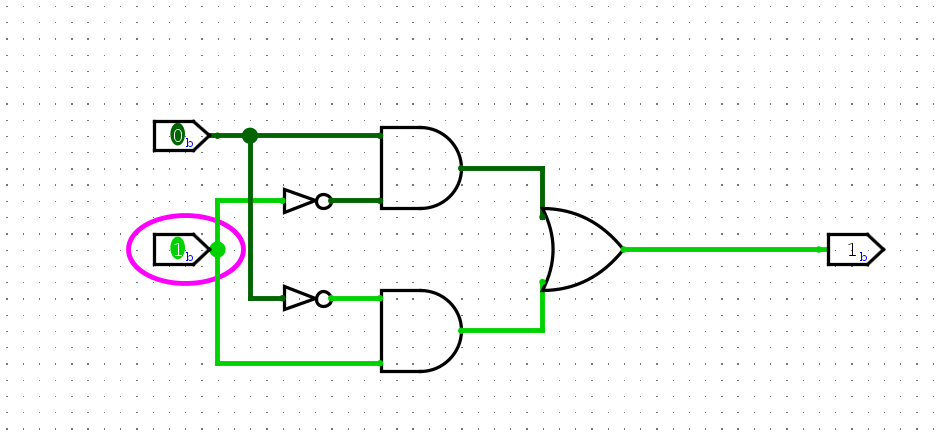

搭建2-4译码器

n选1译码器由 n个not门和2^n的n输入and门构成

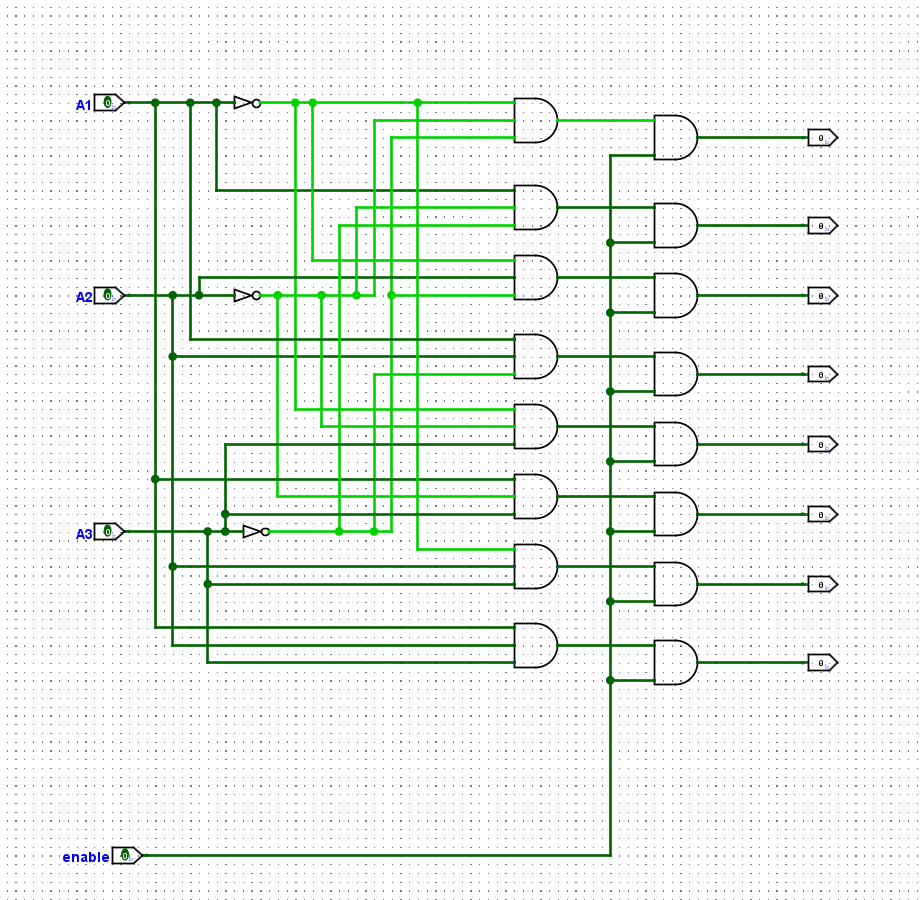

搭建3-8译码器

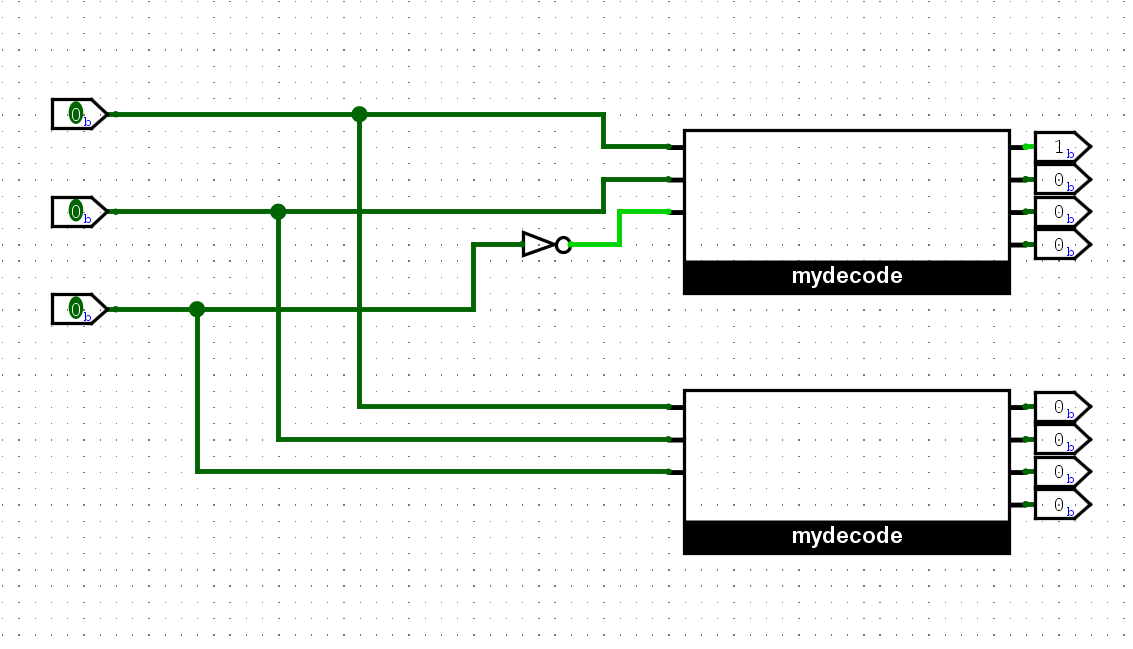

3-8译码器可以通过两个2-4译码器去实现。

我首先在原先的2-4译码器部件的基础上加了一个enable的输入,当使能为高电平时这个译码器会正常工作,相反。

将输入中的最高位看做是选择信号,当高位为0时,仅下半部分的 2–4 译码器被使能,其输出对应 Y0–Y3。 当最高位为 1时,仅上半部分的 2–4 译码器被使能,其输出对应 Y4–Y7。

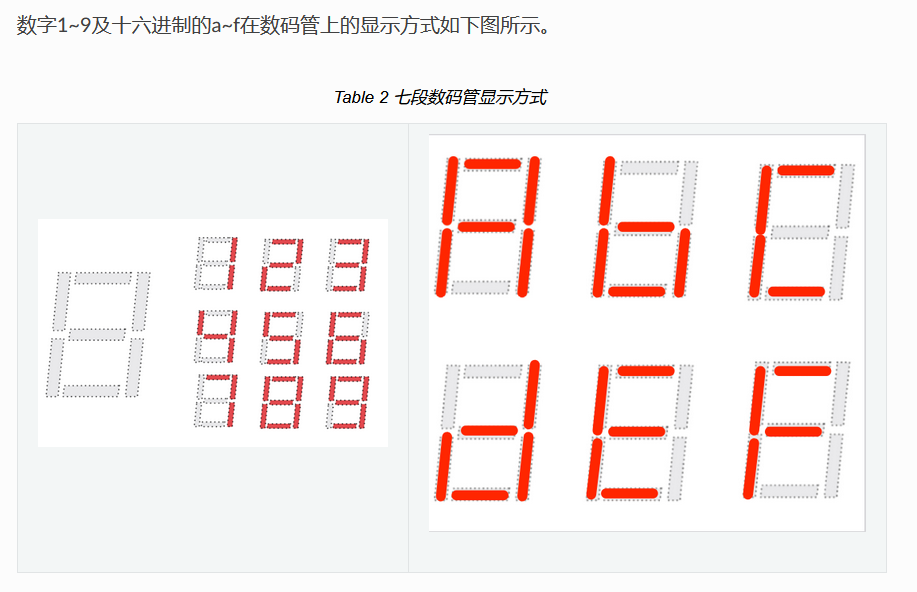

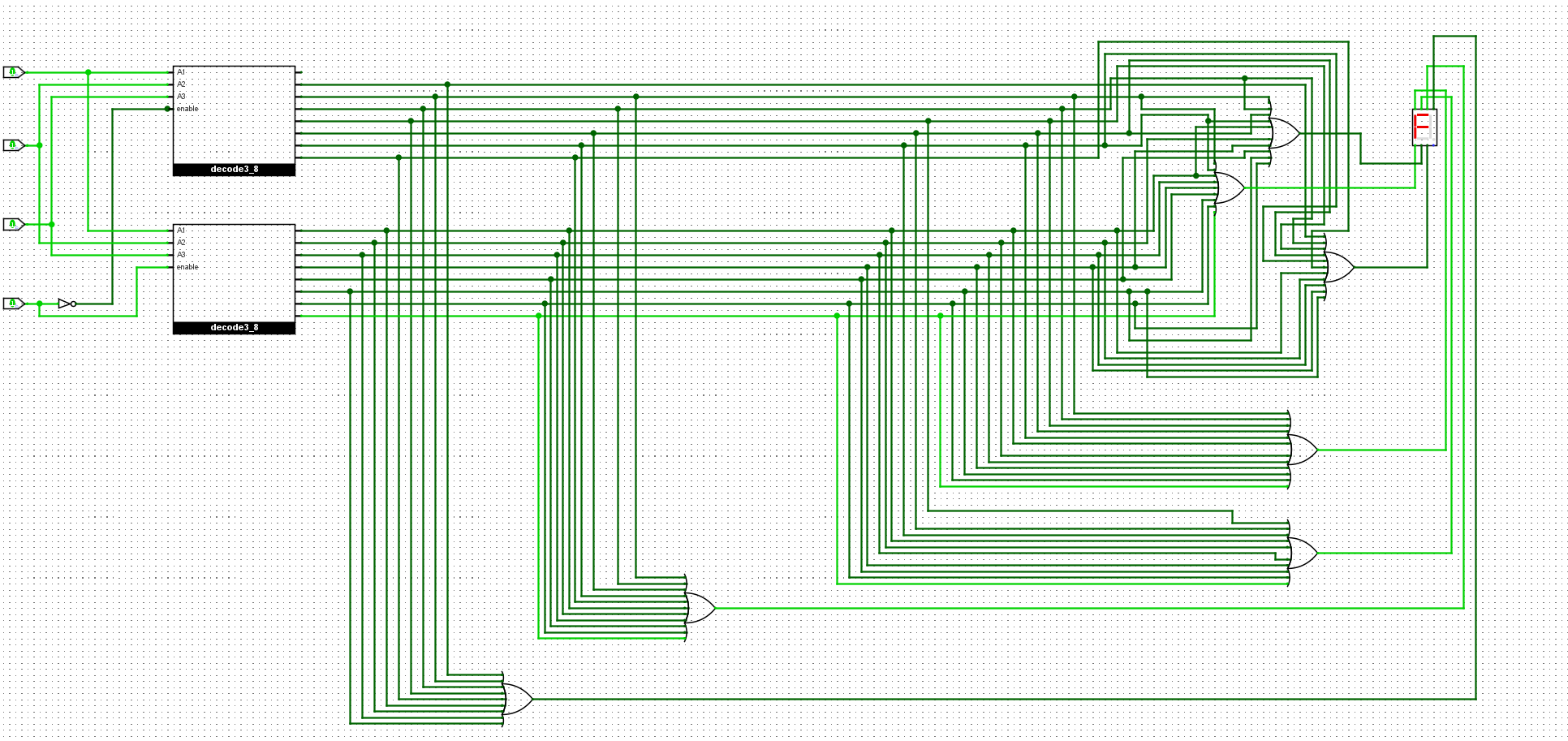

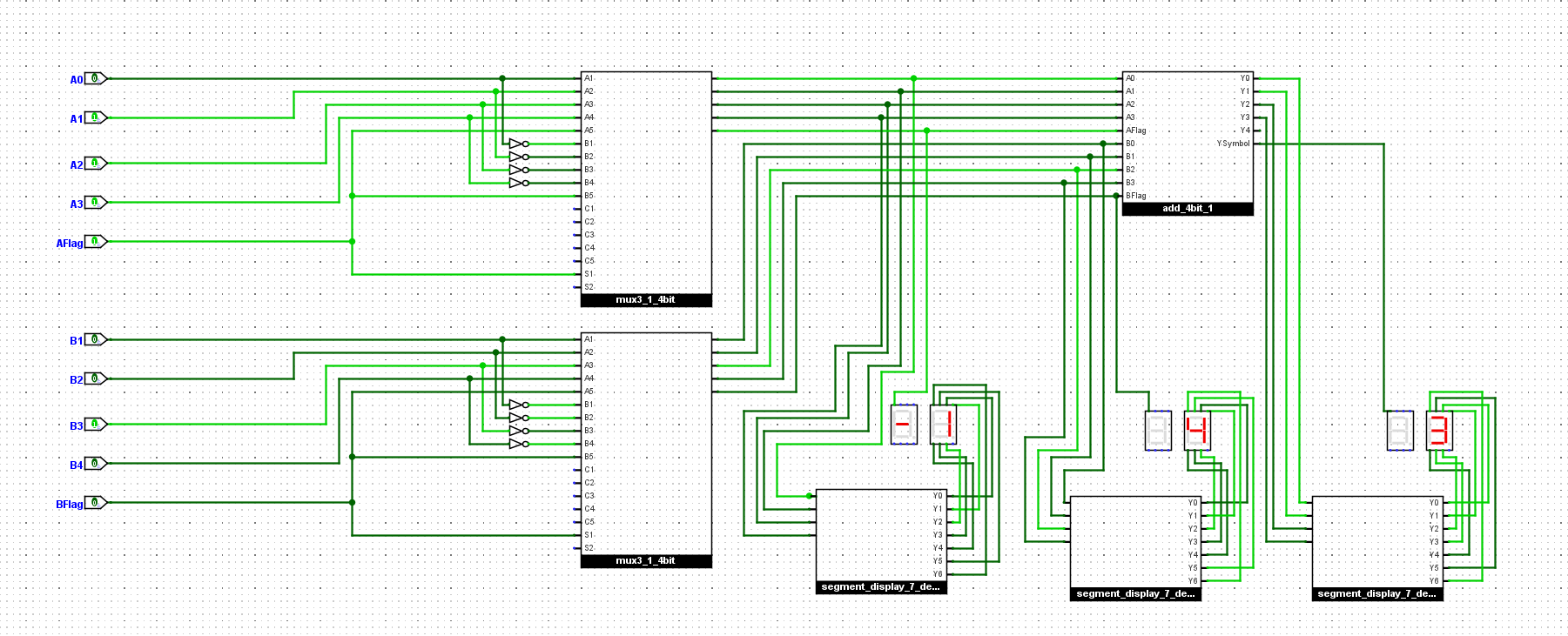

搭建七段数码管译码器

通过两个3-8译码器组合成一个4-16译码器将输入转换为独热码,然后再通过一层或门来决定每个发光二极管在哪些输入情况下应该被点亮就行

3-8译码器

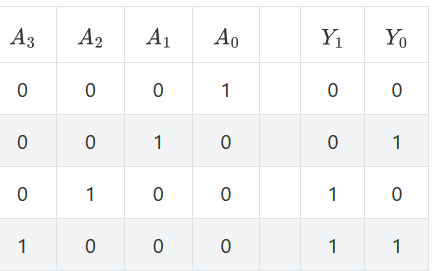

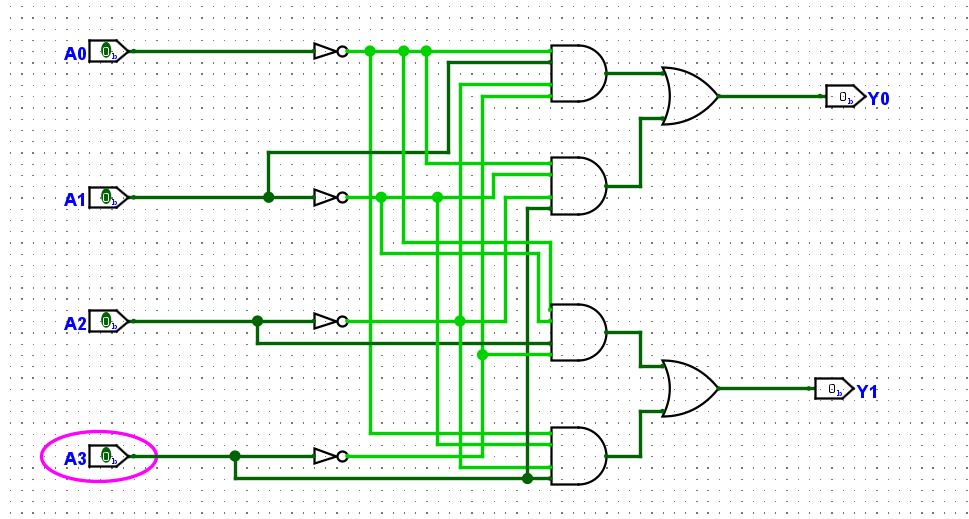

搭建4-2编码器

可以发现Y0的值由A1和A3控制 Y2的值由A2和A3控制

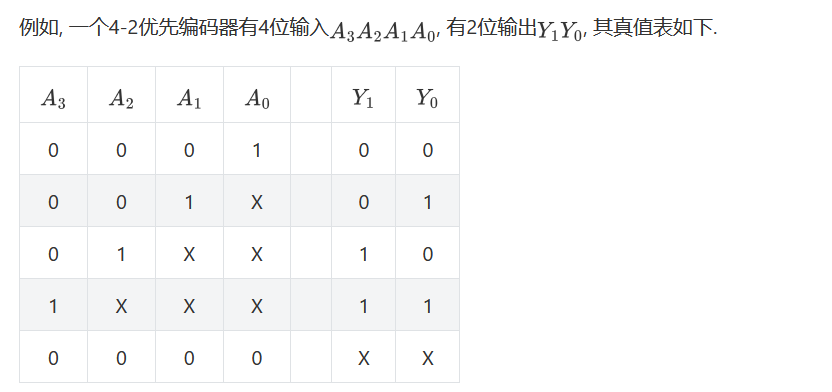

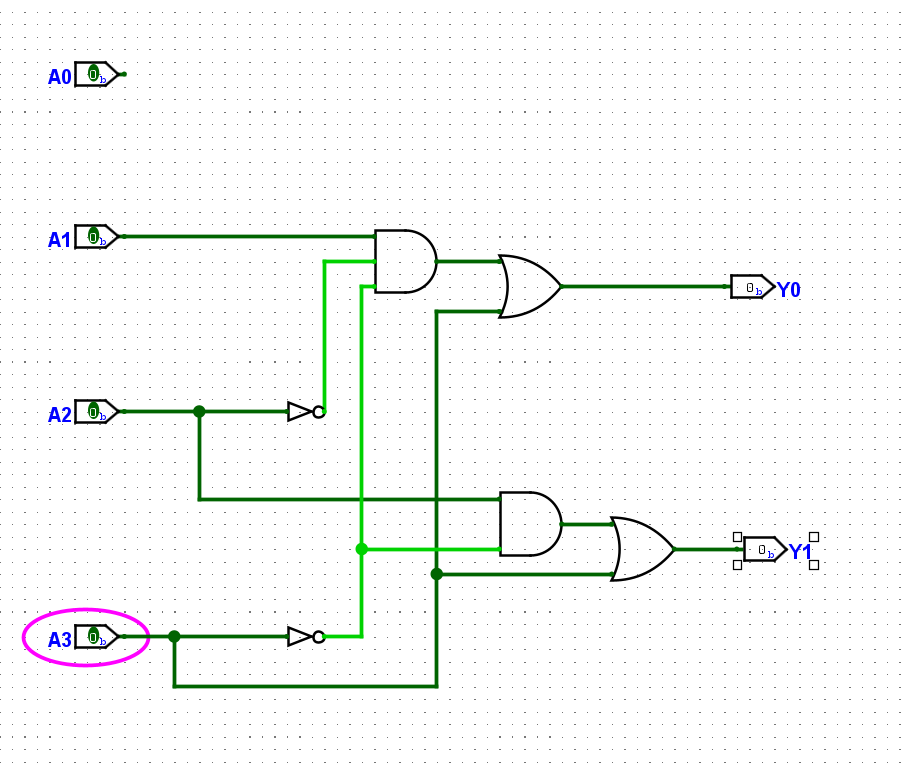

搭建4-2优先编码器

优先编码器就是在编码器的基础上,只看数据的最高位1,忽略之后的低位。

4-2编码器需要用到 (4 + 4 + 2) = 10个逻辑门

4-2优先编码器需要用到(2 + 2 + 2) = 6 个逻辑门

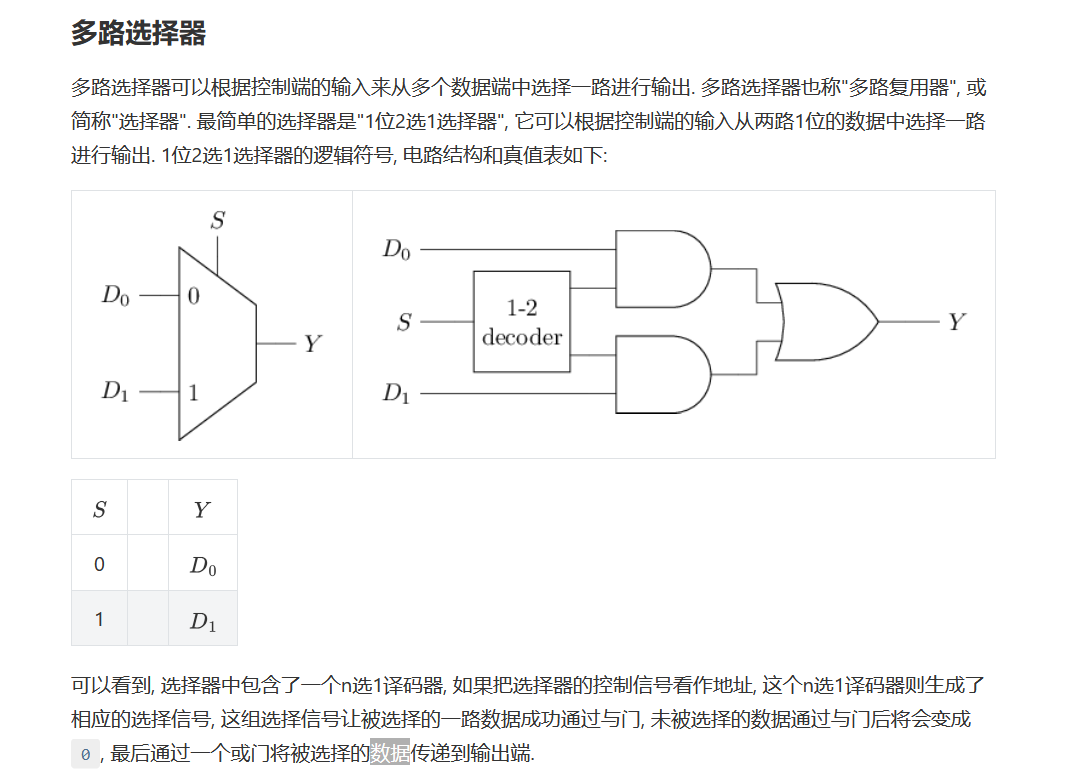

搭建1位2选1选择器

选择器工作原理

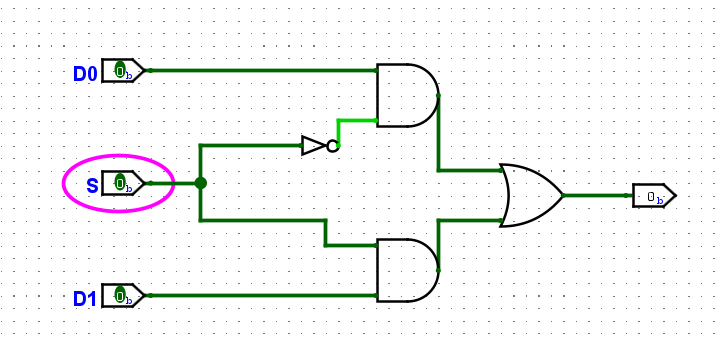

搭建3位4选1选择器

搭建3位4选1选择器,首先需要设计一个2-4译码器去表示四种不同的选择状态,然后将这些选择状态分别与四个输入中的三个单独的比特位进行与运算,类似于使能??然后再用或运算去整合四组加了使能的三个比特位。

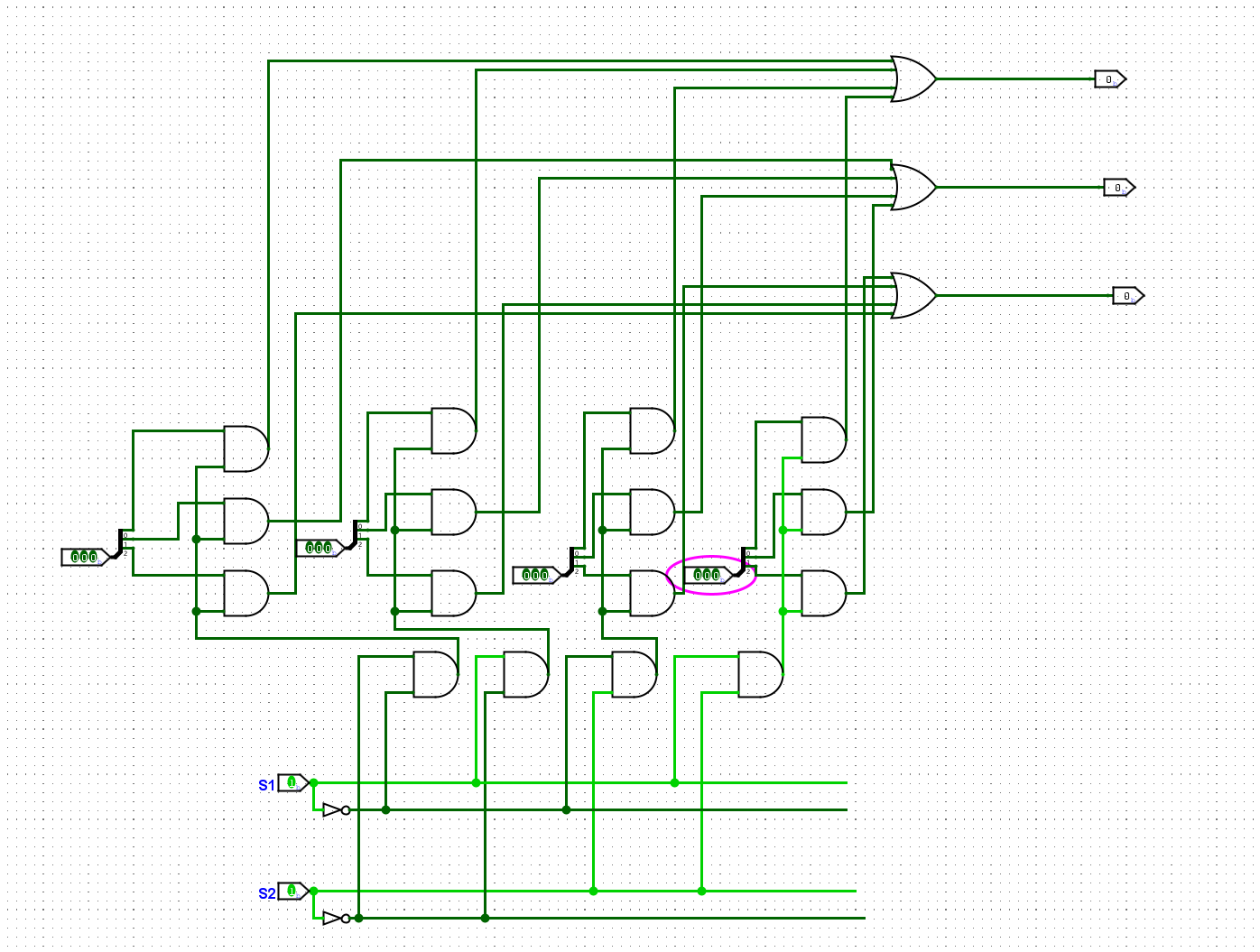

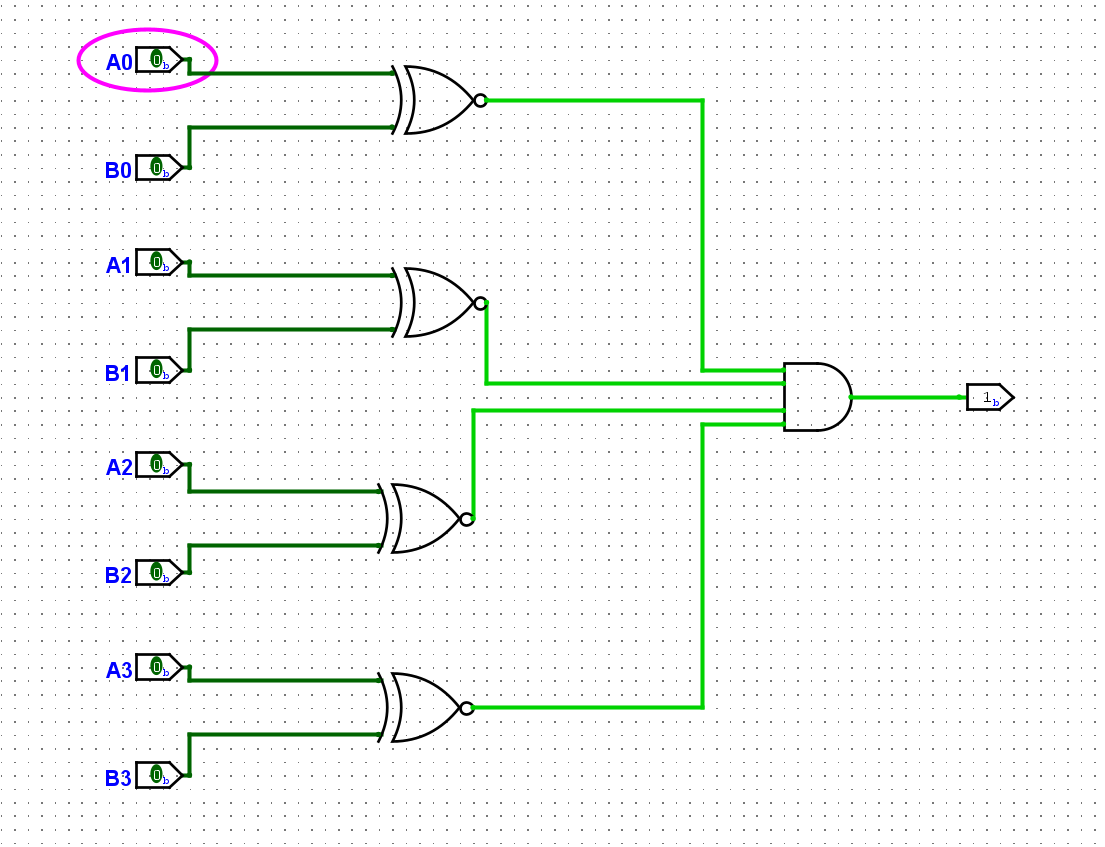

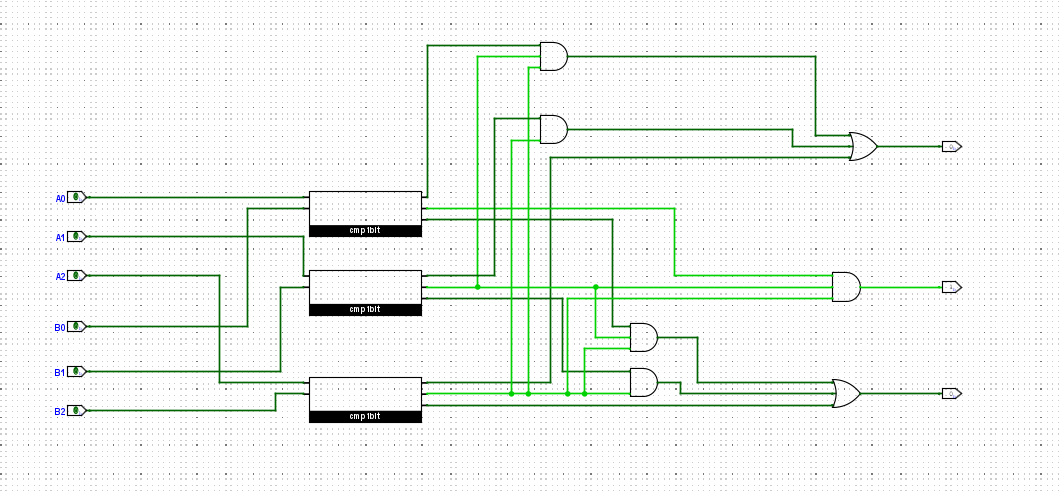

搭建4位比较器

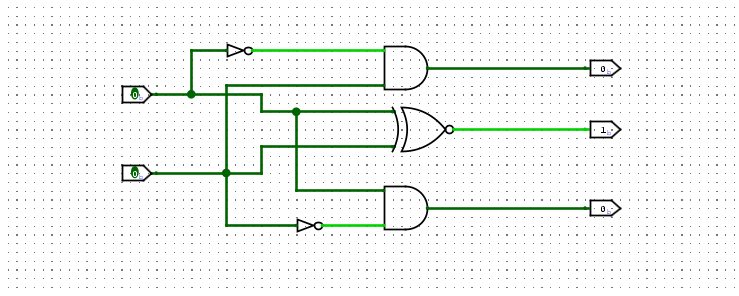

具有大小输出的1位比较器

具有大小输出的3位比较器

使用优先编码器的思想,先从高位开始判断,然后再依次往下判断

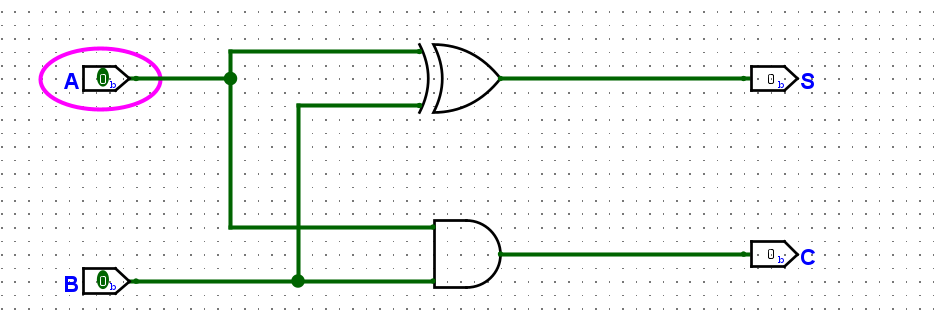

加法器 - 半加器

A |

B |

S |

C |

|

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 |

数据位S 可以通过异或来判断是否有数据 S = A ^ B

进位C 可以通过与运算来判断是否进位 C = A & B

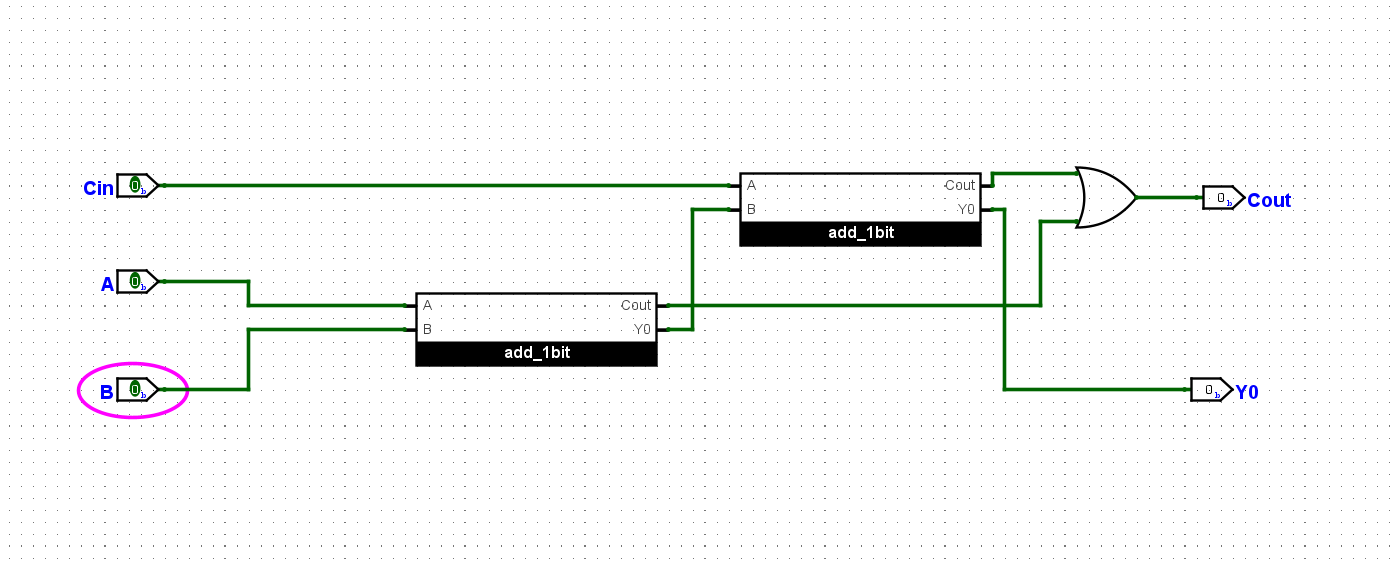

通过两个半加器搭建全加器

全加器本质上是一个三位数的加法,有三个输入和两个输出,两个操作数输入 一个进位输入,一个进位输出和一个数据位的输出,依次计算 Result1 = A + B Result = Result1 + Cin,只要其中一个半加器产生了进位输出,那就会影响全加器Cout的结果

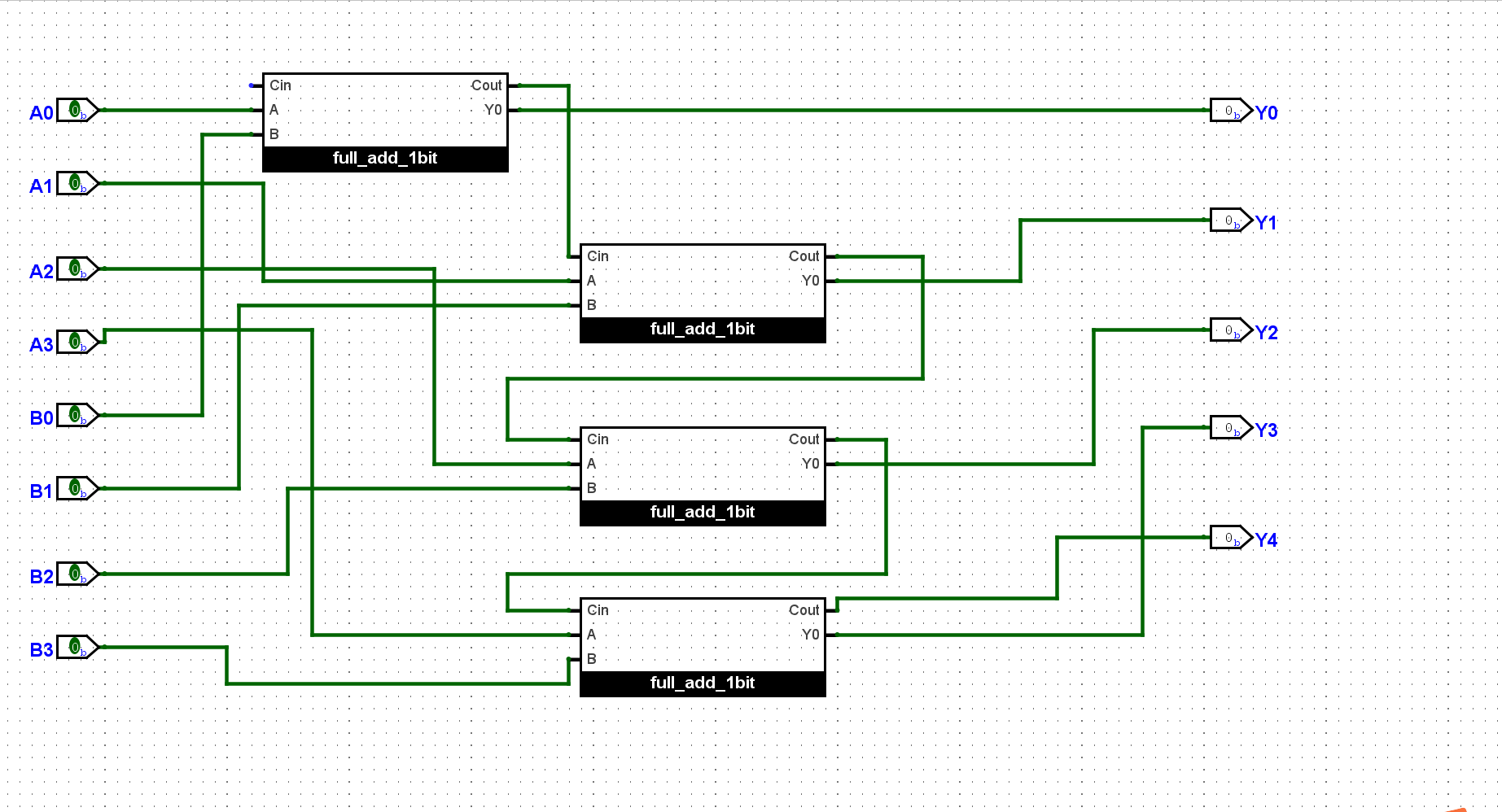

4位加法器

构建4位加法器只需要4个全加器,将上一个全加器的进位输出当做下一个全加器的进位输入,然后第四个全加器的进位输出可以当做一个数据位

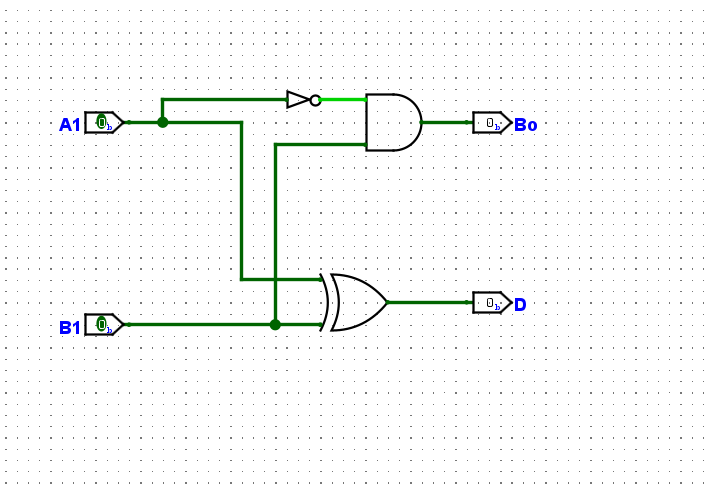

1位半减器

Bo是指借位标志,D是指两个操作数直接的差值

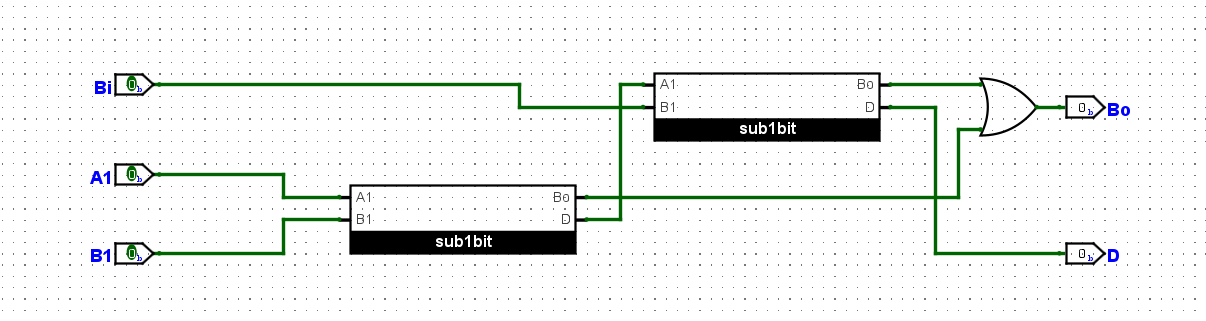

1位全减器

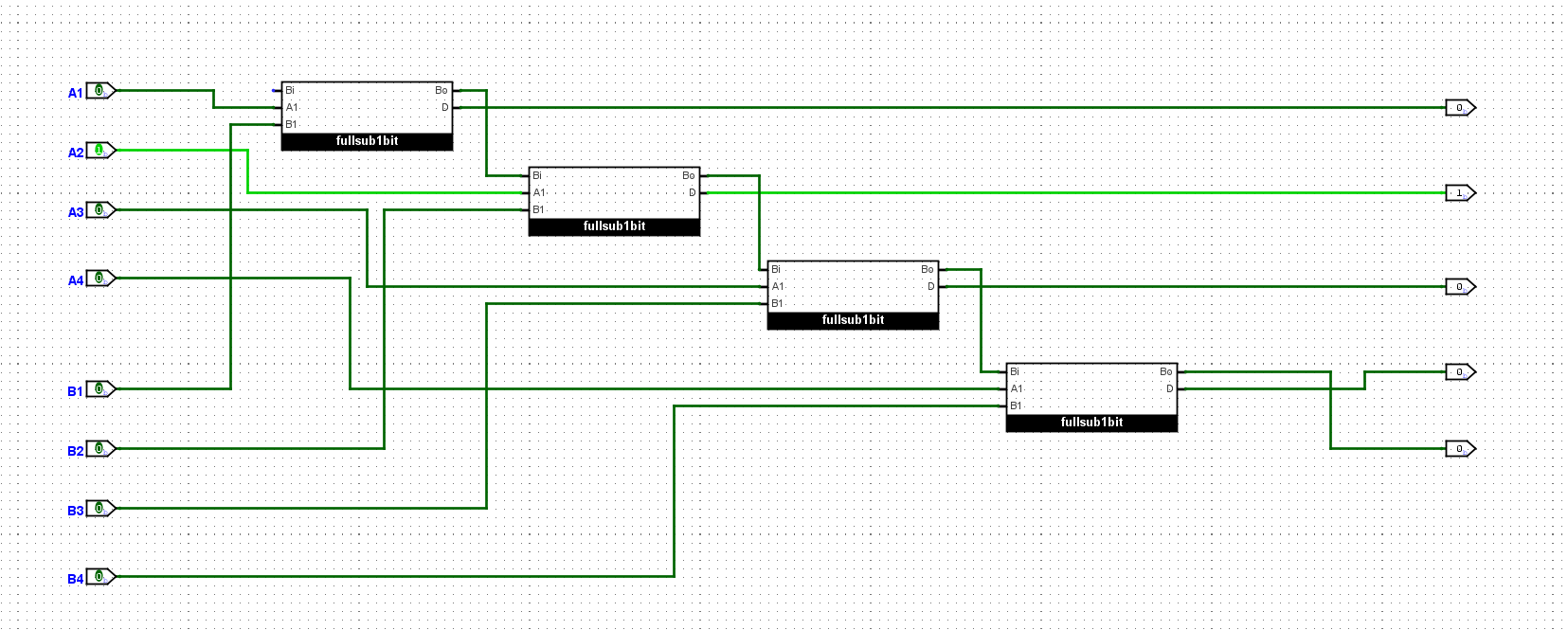

4位减法器

4位减法器只需要在1位全减器的基础上,把每次减法后的借位标志传递给下一个全减器就好了,不过会存在一个问题,如果被减数小于减数的话,那就会存在借位借不完,高位全是1的情况,所以要避免输入的被减数小于减数的情况

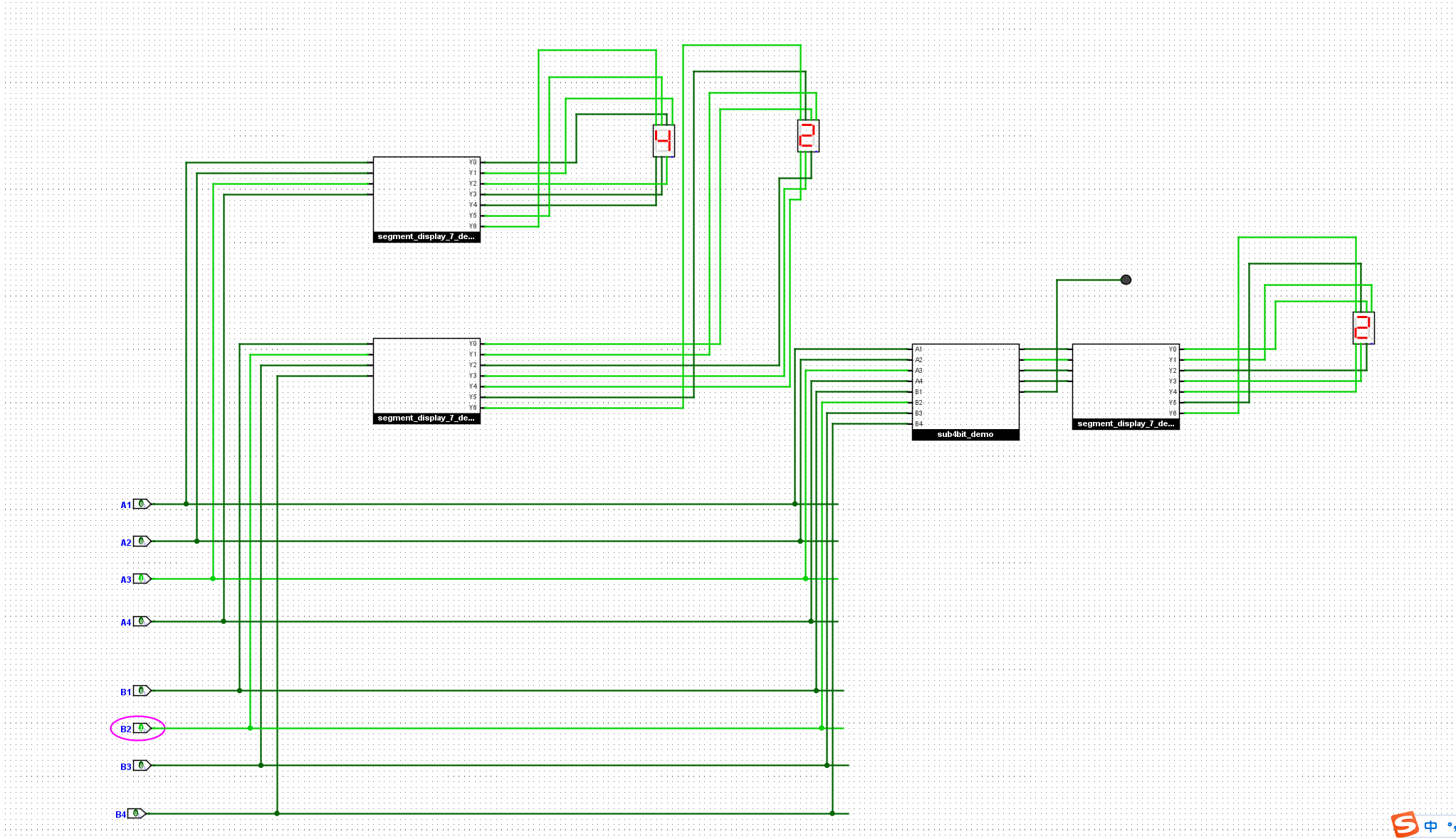

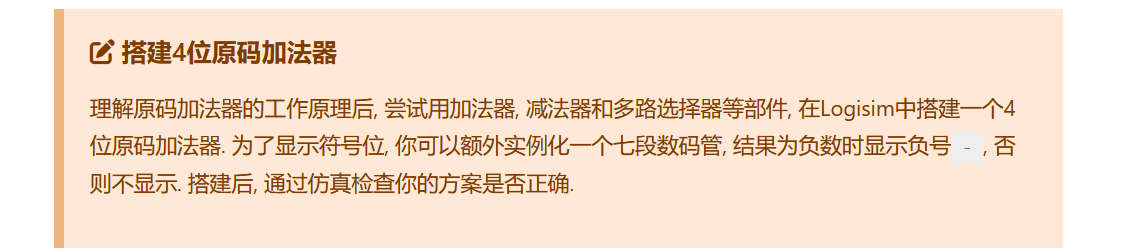

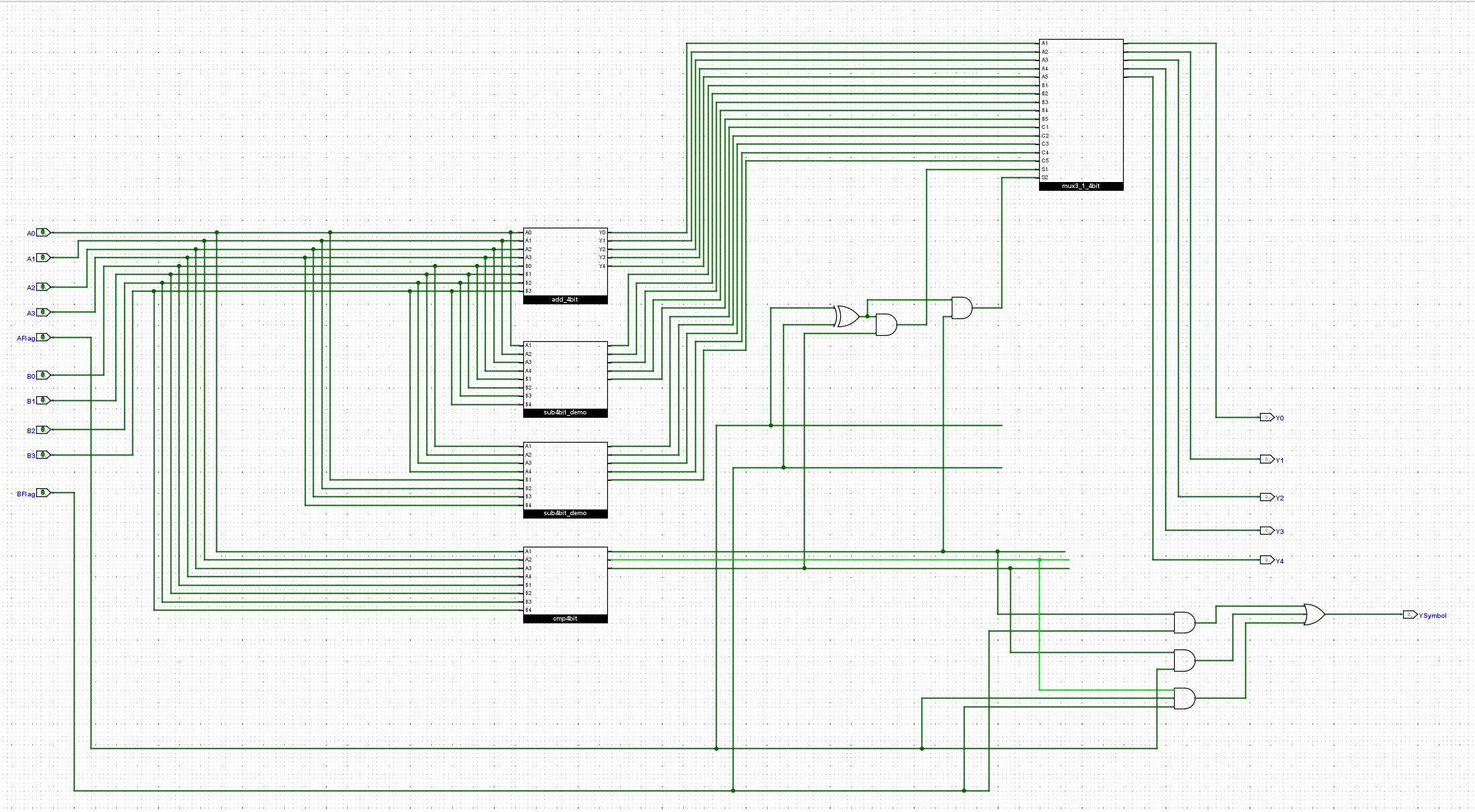

4位原码加法器

原码是一种表示有符号数的编码,当符号位为1时表示负数,相反。

原码的加法规则是这样的,当符号位相同,即两个操作数同时是正数或者负数那就直接用加法来处理,然后取其中一个操作数的符号位,符号位不同的情况下,将绝对值最大的数作为被减数,用减法器去处理计算,处理完成后的结果的符号位取绝对值最大数的符号位,如果两数相同的话,那就取两个符号位的与(意思是两数相同的情况下只有两个操作数都为负数,符号位才为1)

所以实现4位原码的加法,需要实现一个4位的加法器以及两个4位的减法器,用于计算两数绝对值的差,由于减法器的功能是由”借位”来实现的导致被减数不能小于减数,所以需要两个减法器来实现绝对值差值的计算,还有一个用于比较两个数大小的4位选择器和3选1 4位选择器用于实现 “判断两个操作数绝对值大小” “交换操作数位置”,即两个操作数符号不同时 A > B 时 选择 A - B的减法器作为输出,A < B 时 选择 B - A的减法器作为输出

搭建4位反码加法器(通过将反码转换成原码利用原码加法器实现)

只需要在两边输入串上一个4位的2选1选择器,来实现根据符号位判断是否置反输入来实现负数情况下的的反码转原码,之后复用之前实现的4位原码加法器就好了

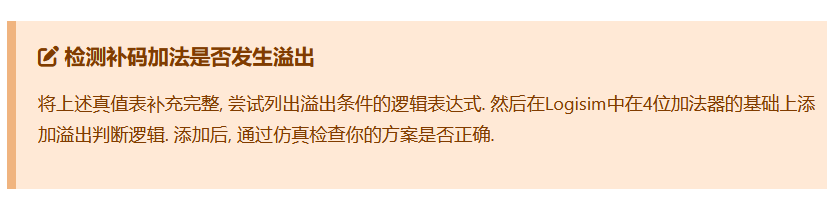

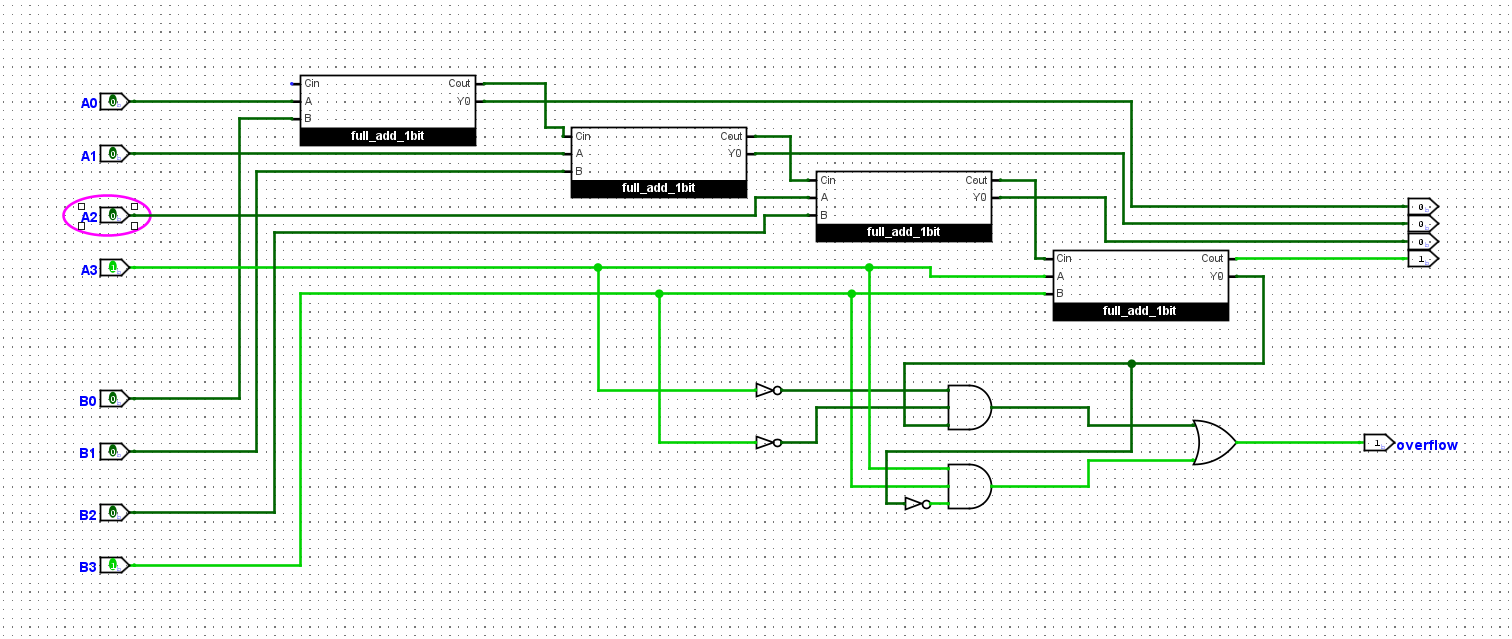

补码加法溢出检测

| An-1 | Bn-1 | Cn-1 | Cn | Sn-1 | 溢出 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 否 |

| 0 | 0 | 1 | 0 | 1 | 是 |

| 0 | 1 | 0 | 0 | 1 | 否 |

| 0 | 1 | 1 | 1 | 0 | 否 |

| 1 | 0 | 0 | 0 | 1 | 否 |

| 1 | 0 | 1 | 1 | 0 | 否 |

| 1 | 1 | 0 | 1 | 0 | 是 |

| 1 | 1 | 1 | 1 | 1 | 否 |

根据真值表可以发现,只需要判断 NOT(An-1) &NOT(Bn-1)&Sn-1 + An-1&Bn-1&NOT(SN-1)这组条件就好了

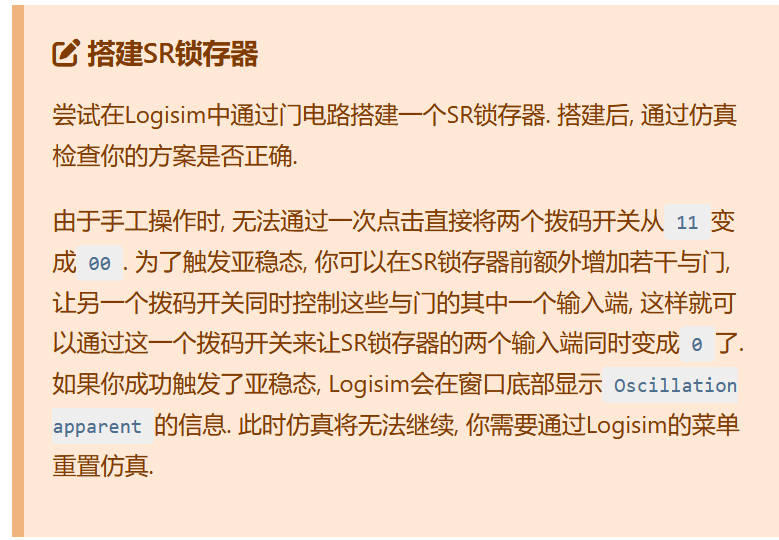

sr锁存器

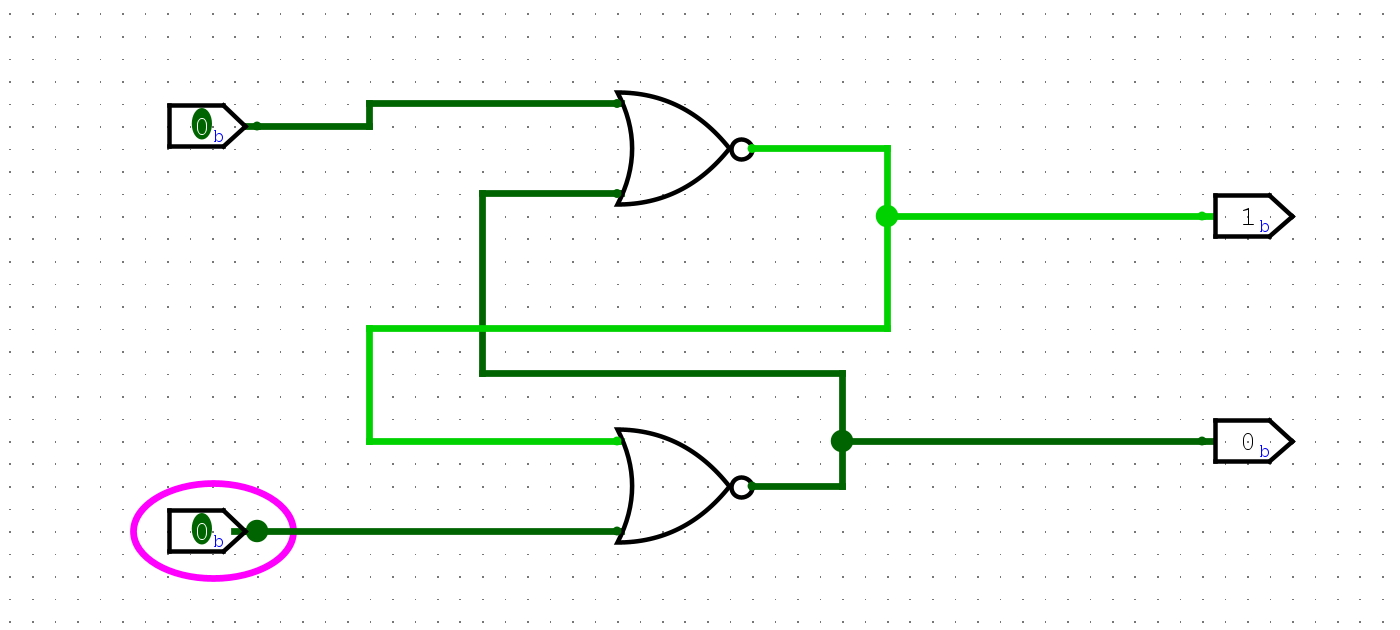

搭建sr锁存器并触发亚稳态

sr锁存器由两个或非门构成,二输入或非门的性质是,将其中一根引脚看做是控制信号,当控制信号为0时,或非门处理另一个输入的行为类似于一个非门,会置反输入逻辑。当控制信号为1时,输出行为恒等为0,

触发亚稳态

将s r的输入从11切换到00,由于交叉配对反相器的性质 输出会在 00 11之间反复震荡进入亚稳态

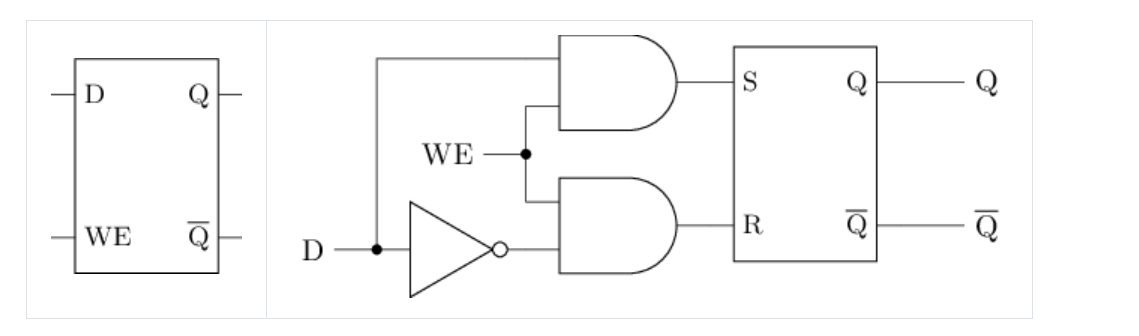

D锁存器

分析D锁存器的行为

D锁存器就是在sr锁存器的基础上添加了若干门电路,有一个写使能的输入和一个数据位的输入

若干门电路的行为逻辑分析

| D | WE | S | R |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

可以发现当D锁存器的写使能为0时,sr锁存器保持锁存的状态,当写使能为1时,会根据D的状态去更新sr锁存器中的数据

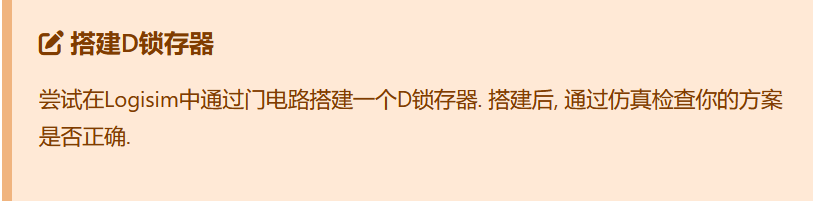

搭建D锁存器

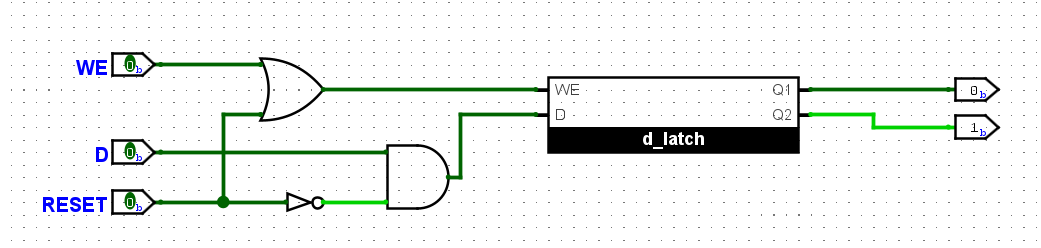

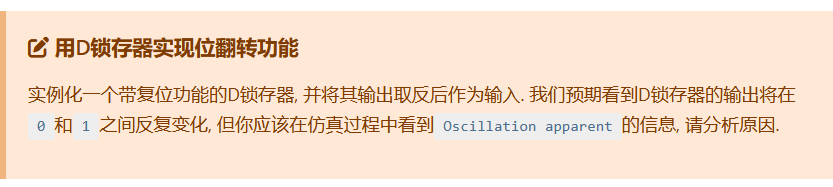

搭建带复位功能的D锁存器

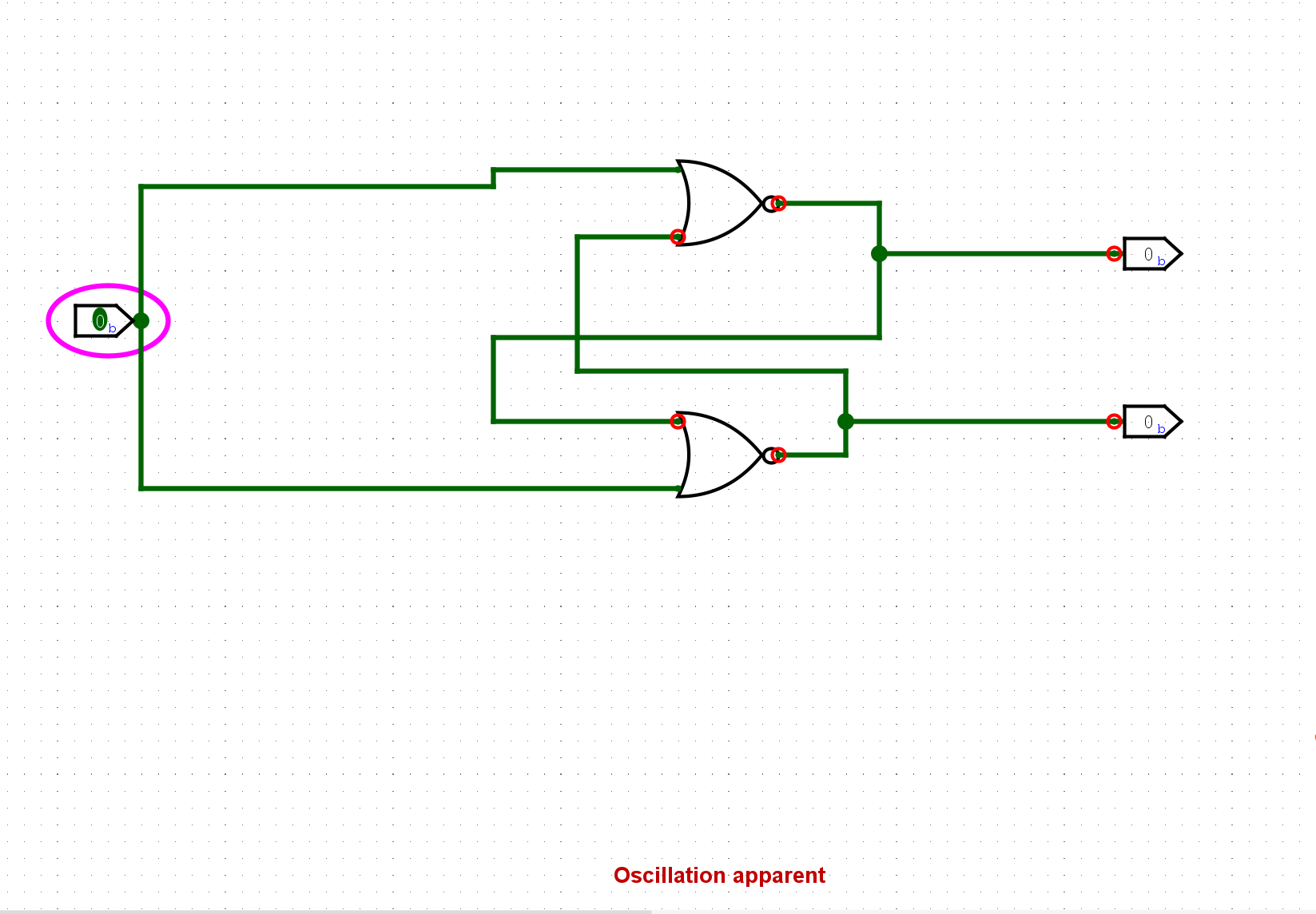

用D锁存器实现位翻转功能

写使能为1时,其输出取反后作为输入,等价于将非门的输出连接到输入,输入为1时,经过一次置反下一次输入为0,再经过一次置反为1,会不断循环下去,所以会出现 0和1直接反复震荡这样的现象

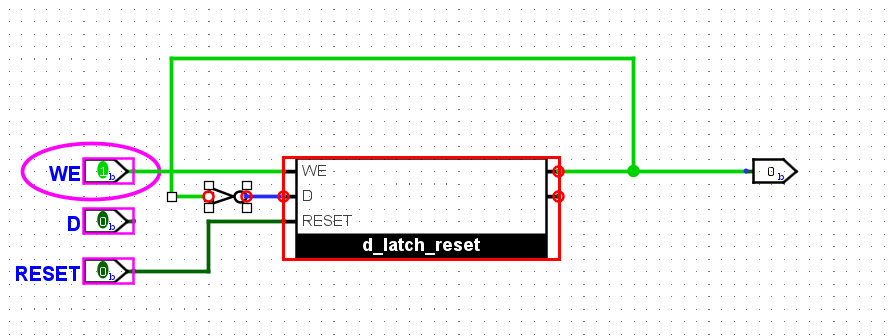

搭建D触发器

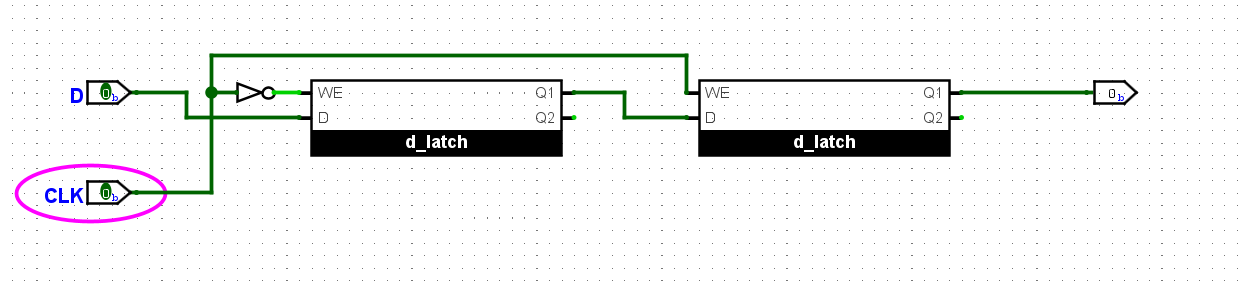

搭建带复位功能的D触发器

复位功能的实现只需要在reset为1时往两个D锁存器中写入0数据就好了,在原先的D锁存器数据位输入那加一个选择器,通过RESET来控制,然后写使能那串一个或门

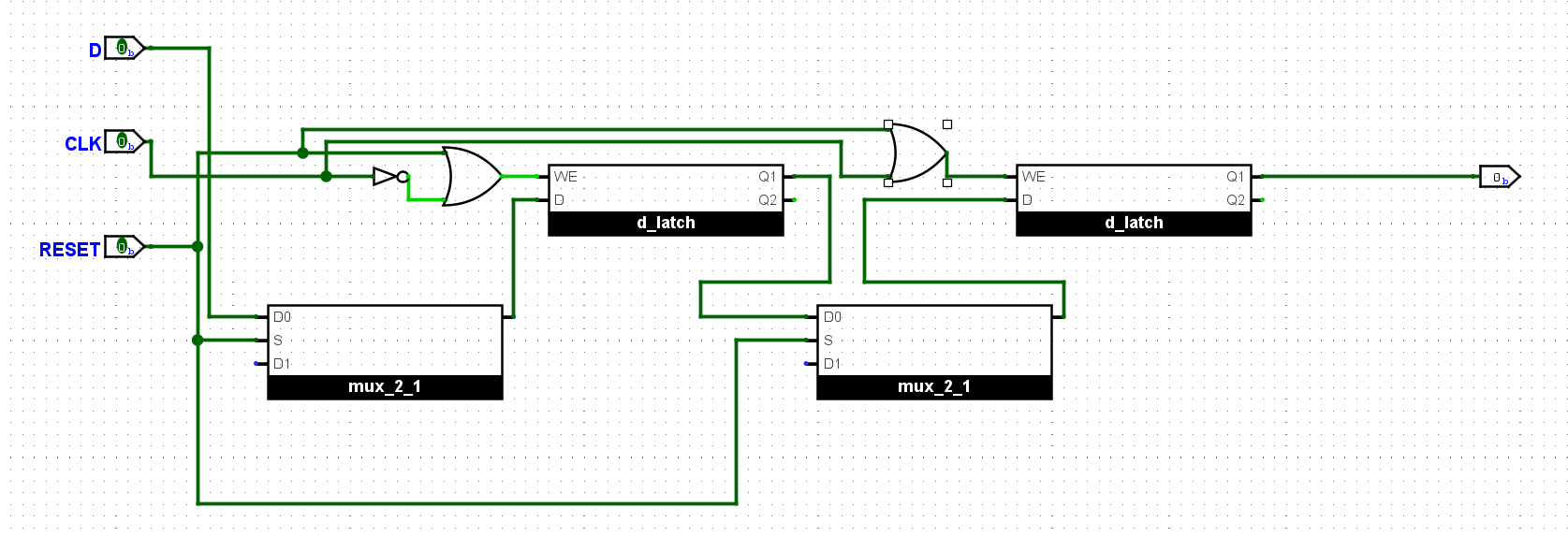

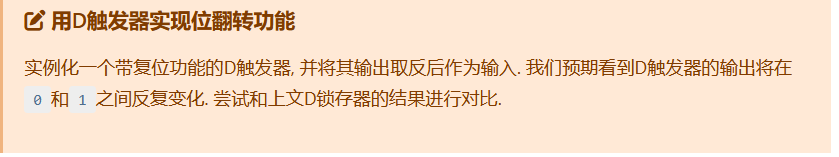

D触发器实现位翻转功能

D锁存器在写使能开启的时候,将其输出取反作为输入本质上是一个非门,处于亚稳态的一个状态,D触发器应该是实现不了这种0 1 反复震荡的状态,只有处于上升沿这一阶段才会往里面写入输出置反的数据

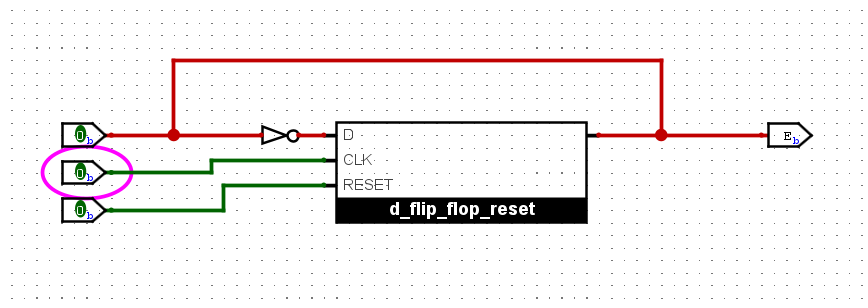

搭建带使能端的D触发器

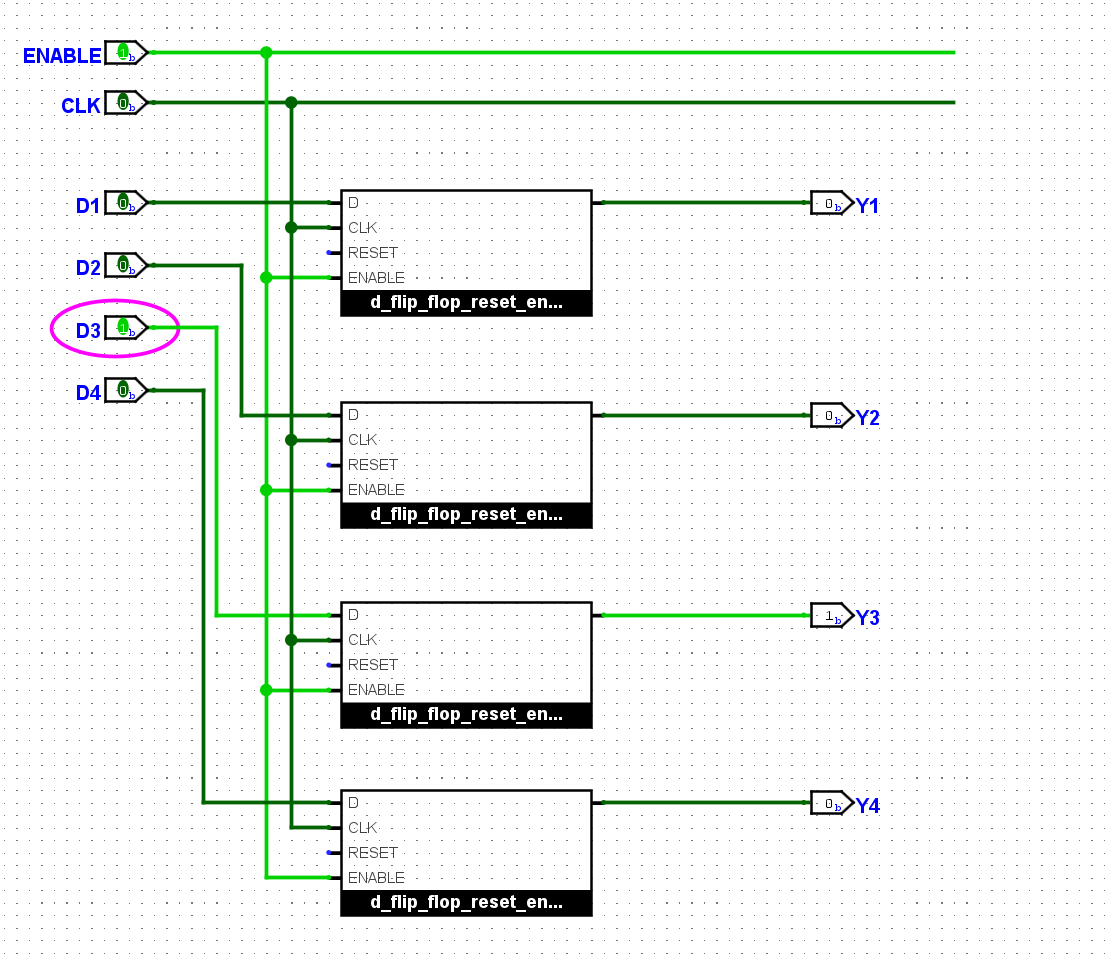

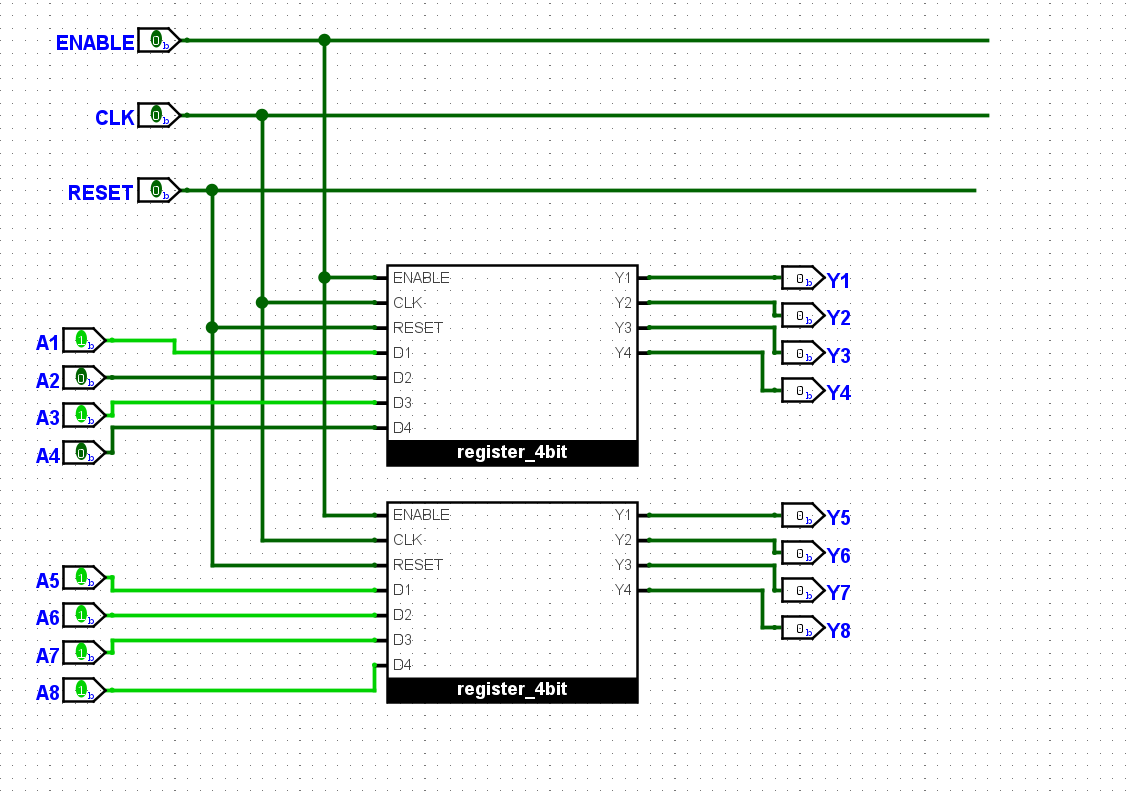

搭建4位寄存器

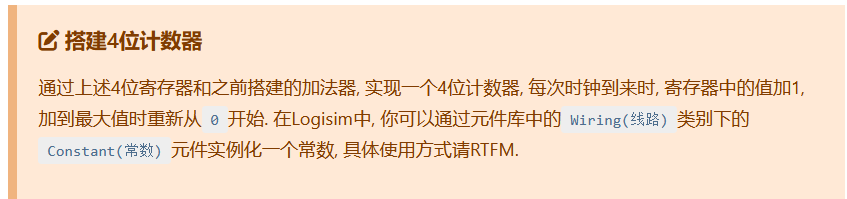

搭建4位计数器

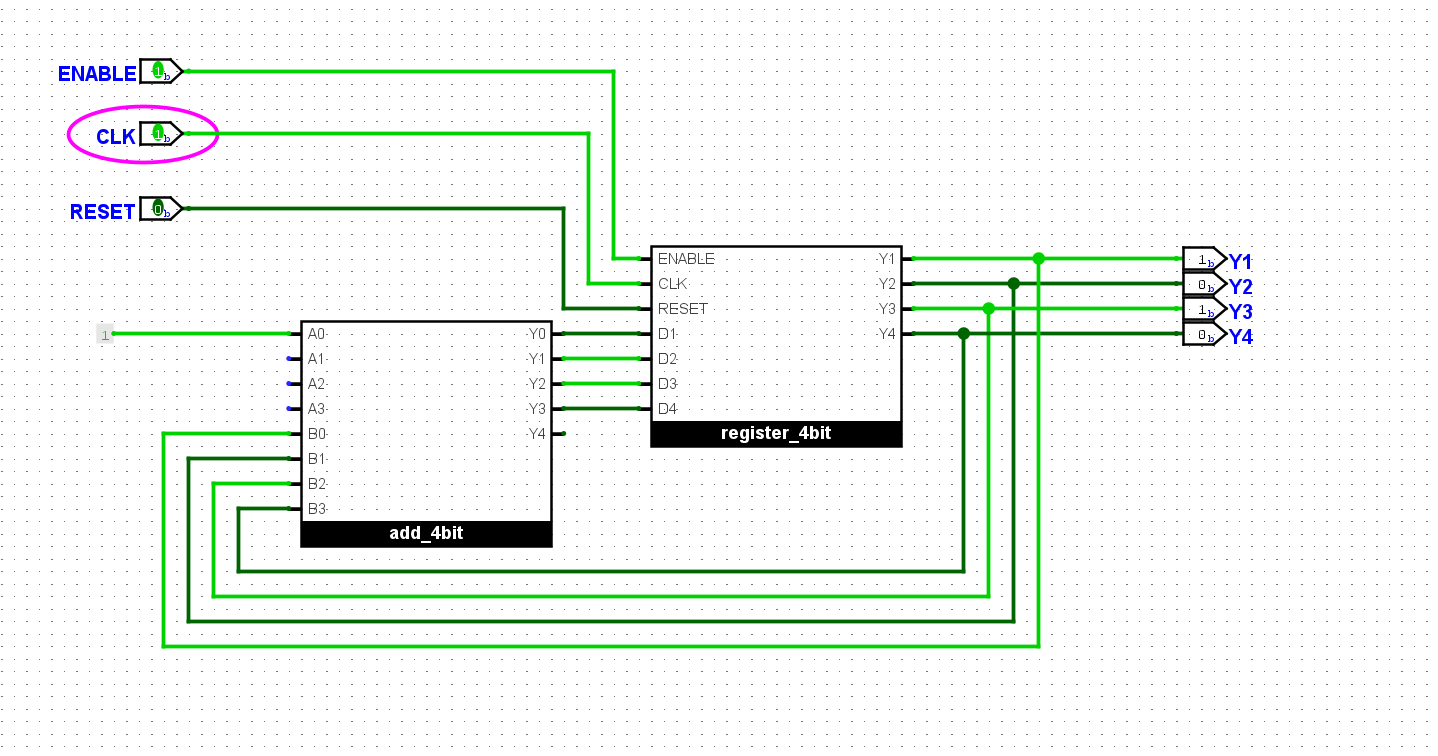

8位寄存器

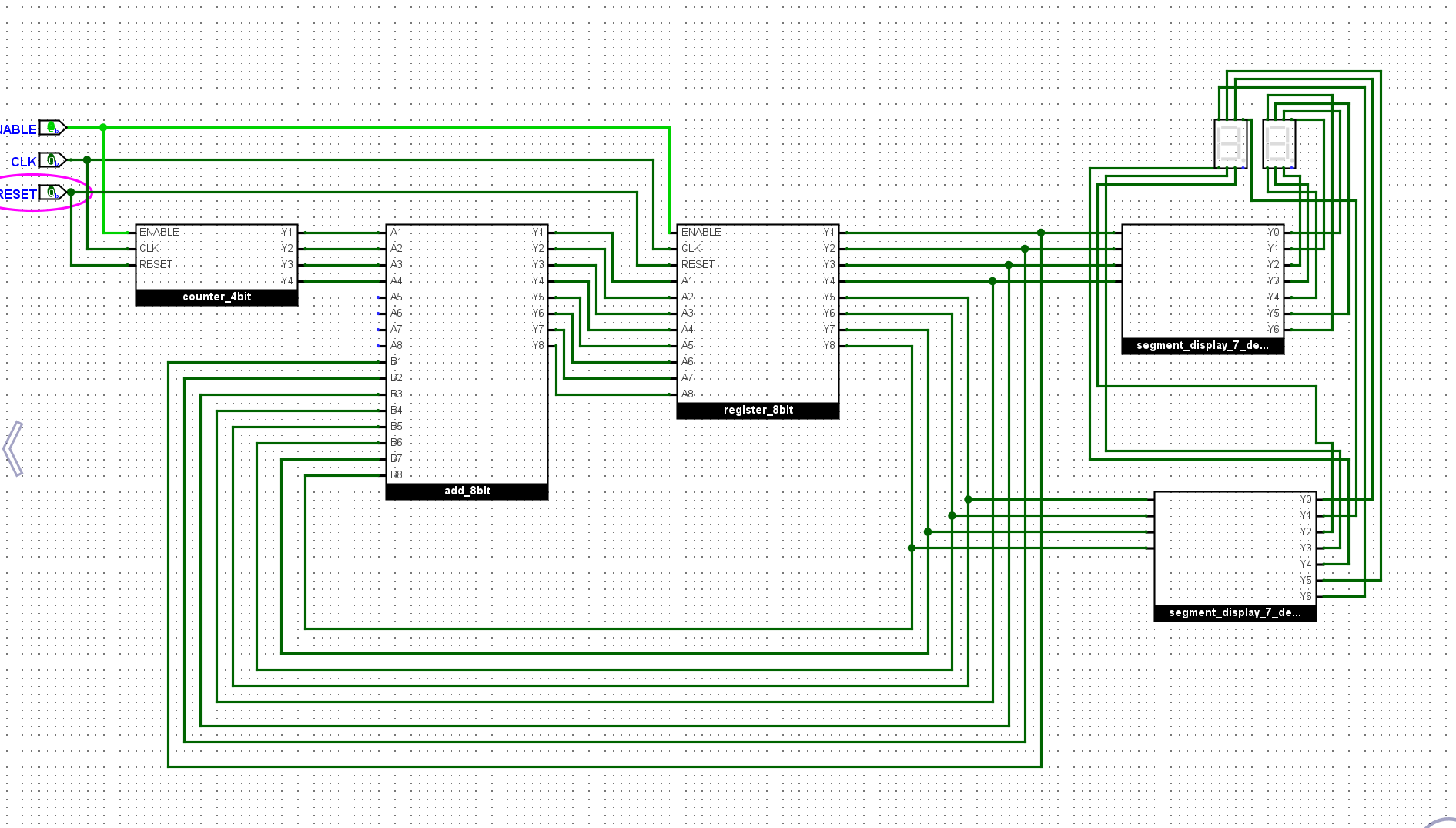

设计数列求和电路

数列求和电路只需要一个计数器一个加法器和一个寄存器,每次上升沿更新寄存器的值为 久的寄存器的值+计数器的值

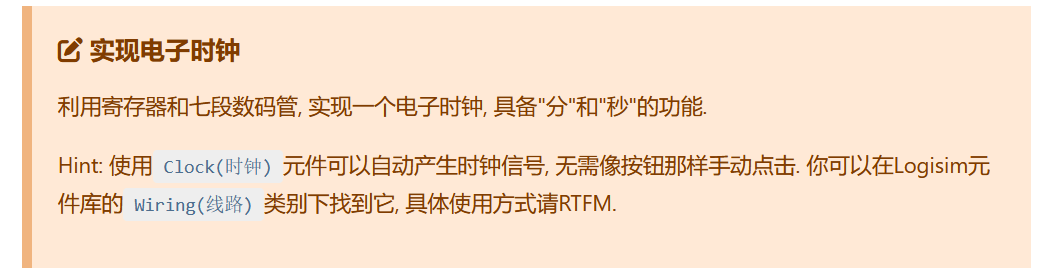

实现电子时钟